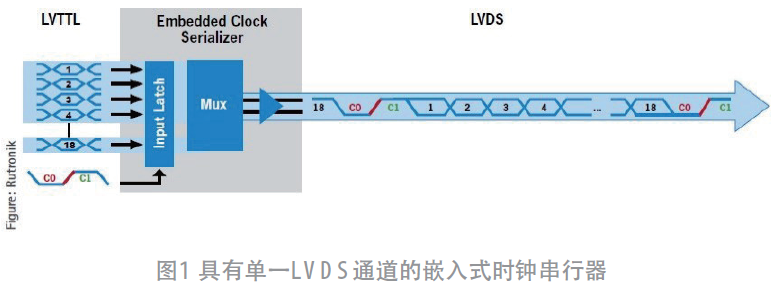

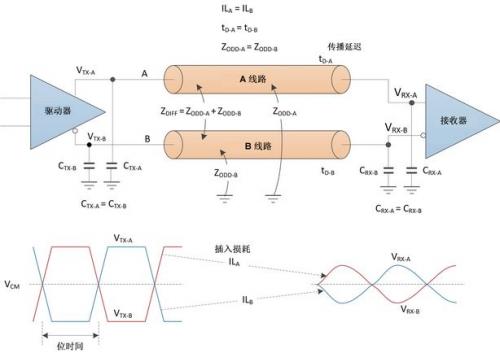

接口定义LVDS是一种低压差分信号技术接口,低压差分信号传输:输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。接口类型a.单6位LVDS输出接口。这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或18bit LVDS接口。b.双6位LVDS输出接口。这种接口电路

关键字:

信号技术 通信原理 LVDS

株式会社村田制作所推出了1210尺寸静噪元件共模扼流线圈“DLM11CN_HH2系列”新产品,适用于汽车中的LVDS、SerDes、USB、HDMI等高速差分接口——其中LVDS(Low Voltage Differential Signaling)是液晶面板用接口,SerDes(Serializer/Deserializer)则用于串行和并行信号互换的电路。本新产品已从2024年12月起开始批量生产。在汽车市场,随着高级驾驶辅助系统(ADAS)和自动驾驶(AD)的发展,汽车周围检测用相机、以及通过激光束

关键字:

高速差分接口 LVDS

信号链是连接真实世界和数字世界的桥梁。随着ADC采样率和采样精度的提升,接口芯片的信号传输速度也越来越快,高速信号传输的各种挑战慢慢浮现出来了。作为一个信号链设计或验证工程师,这些基本概念你一定要知道。相比传统的CMOS传输技术,在信号链中引入LVDS或JESD204B,可以实现更高的信号传输速率,更低的功耗,具备更好的抗干扰性 (信噪比更佳),而且线束数量会大幅降低。LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Se

关键字:

信号链 高速信号 LVDS JESD204B

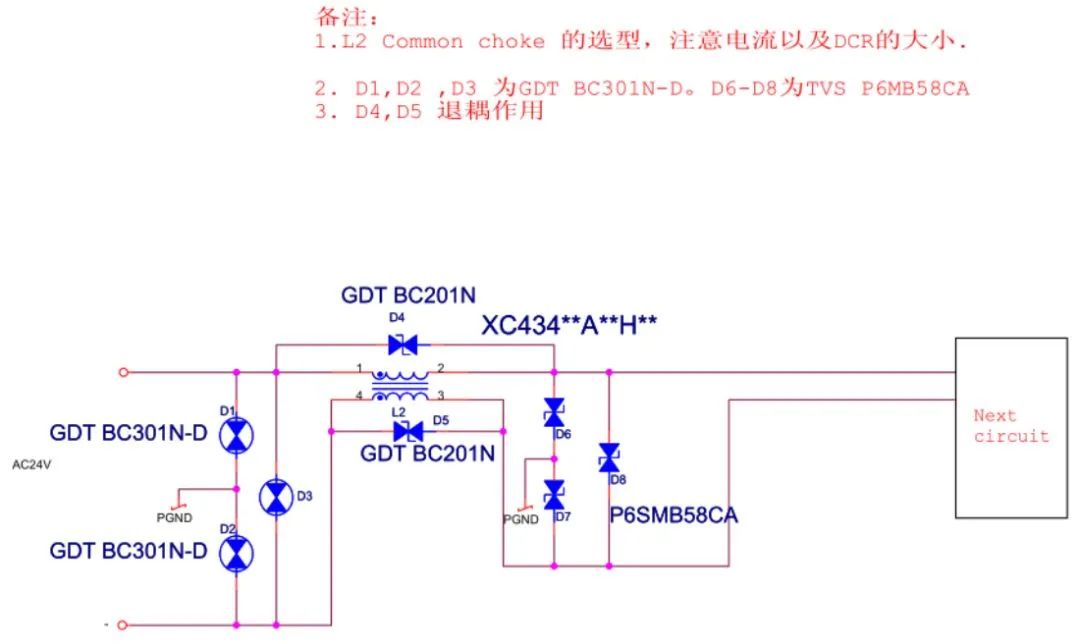

LVDS 数据线接收器采用集成有故障保护偏置电阻的故障保护偏置网络设计。为了提高其抗噪能力并增强其故障保护操作的可靠性,本文将帮助您了解如何在网络中添加和计算额外的故障保护偏置电阻。还提供了在其驱动器和接收器卡上采用 ESD 二极管网络的应用示例。LVDS 数据线接收器采用集成有故障保护偏置电阻的故障保护偏置网络设计。为了提高其抗噪能力并增强其故障保护操作的可靠性,本文将帮助您了解如何在网络中添加和计算额外的故障保护偏置电阻。还提供了在其驱动器和接收器卡上采用 ESD 二极管网络的应用

关键字:

LVDS

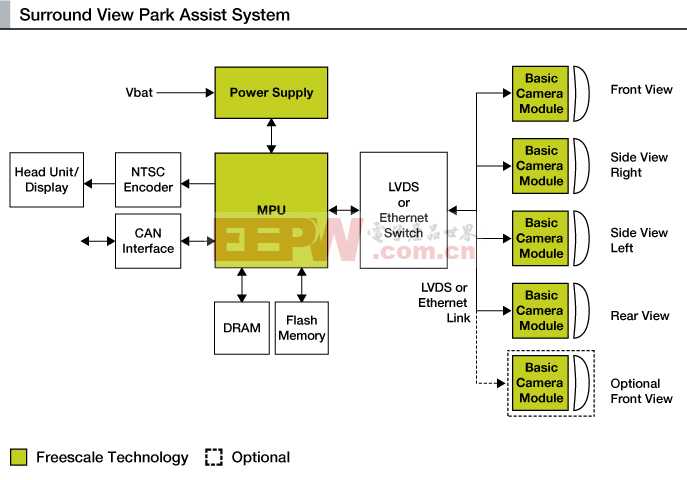

早于2018年,美国就规定所有汽车、SUV、卡车和厢式货车必须配备后视视野系统。事实上,直至最近,后视摄像头仍然是许多车型配备的唯一摄像头,并被视为一项出色的安全功能。过去几年间,汽车不断进化,增加了各种各样创新的安全功能,包括盲点检测、环绕监控、前后碰撞警告、车道保持辅助和自动停车辅助等。这些功能利用摄像头和传感器,帮助驾驶员通过仪表盘显示屏了解汽车及周围环境。高端车型至少会配备六个摄像头。车内可能还会配备视频显示系统,譬如供乘客使用的DVD播放器和电视。因此,市场对更高速的数据和图像通信的需求也相应激

关键字:

Semtech LVDS

意法半导体(STMicroelectronics;ST)简化新一代小型低轨道(Low-Earth Orbit,LEO)卫星的设计和量产。低成本又可靠的低轨道卫星可以从低地球轨道提供地球观测和宽带网络等服务。 意法半导体推出经济型辐射硬化芯片,用于成本敏感的「新太空」卫星应用ST的新系列辐射硬化电源、模拟和逻辑芯片采用低成本塑料封装,为卫星电子电路提供重要功能。意法半导体甫推出该系列的首批九款产品,其中包括一个数据转换器、一个稳压器、一个LVDS收发器、一个线路驱动器和五个逻辑闸,这些产品用于整个

关键字:

低轨卫星 LVDS ST 意法半导体

越来越多的设备都配备显示器,包括冰箱、智能手表和汽车。用户期望在任何介质上都能够以零抖动的方式实现清晰的播放。即使采用不同的标准,也可以使用桥接集成电路(IC)来做到这一点。低压差分信号技术(LVDS)是快速传输大量数据最知名的差分方法,传输速率高达每秒数Gbit,因而可以处理图像和视频内容。LVDS 技术是National Semiconductor(编者注:已被TI 收购)开发的,美国电子工业协会(EIA)将其标准化为EIA-644 规范。这是许多IC 供应商都在使用的自由开放的标准规范。LVDS 是

关键字:

202107 桥接 LVDS

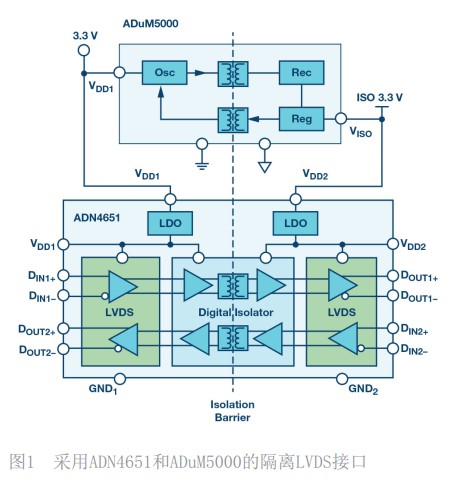

介绍了高速信号传输的挑战,及ADI公司的信号隔离式LVDS缓冲器——ADN4650/ADN4651/ADN46521是,若与ADuM5000组合使用,可实现短距离600 Mbps和数米距离200 Mbps的传输速率。

关键字:

数字隔离 LVDS 接口 201902

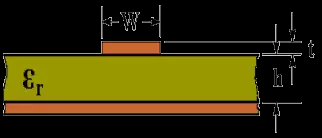

没有阻抗控制的话,将引发相当大的信号反射和信号失真,导致设计失败。常见的信号,如PCI总线、PCI-E总线、USB、以太网、DDR内存、LVDS信号等,均需要进行阻抗控制。阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。 不同的走线方式都是可以通过计算得到对应的阻抗值。 微带线(microstrip line) •它由一根带状导线与地平面构成,中间是电介质。如果电介质的介电常数、线的宽度、及其与地

关键字:

PCB LVDS

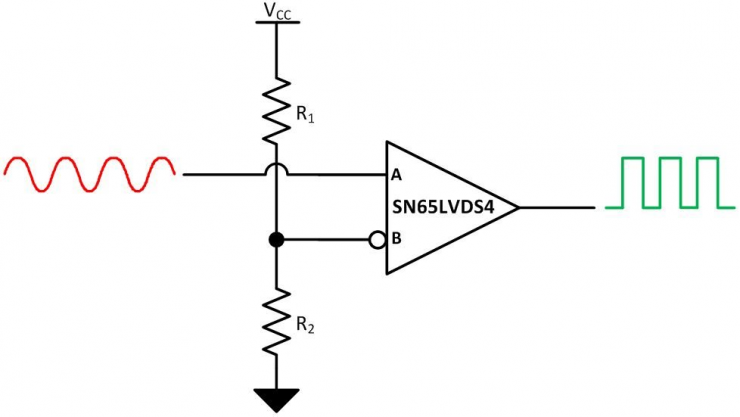

如何用单个赛灵思FPGA数字化数百个信号- 在新型赛灵思 FPGA 上使用低电压差分信号(LVDS),只需一个电阻和一个电容就能够数字化输入信号。由于目前这一代赛灵思器件上提供有数百个 LVDS 输入,理论上使用单个 FPGA 就能够数字化数百个模拟信号。

关键字:

赛灵思 FPGA LVDS

数字电视的发展,使人们对各种高画质影音设备的购买需求激增。FPD TV、DVD播放器、NB、数字相机及数字摄影机都已出现支持Full HD规格的产品。

关键字:

LCD LVDS IC

高速串行互连是标志并行数据总线向串行总线转变的技术里程碑,这种技术是减少设计师面临的信号阻塞问题的方法。这种转变是由业界对系统成本和系统扩展能力的要求所推动的。随着芯片技术的发展和芯片尺寸的缩小,用速率达数千兆位的高速串行互连来取代传统的并行结构变得简单易行。

关键字:

差分信号技术 LVDS FPGA

红外成像导引头采用红外焦平面阵列探测器,易受太阳光等杂散光的影响,评估杂散光对红外探测器成像质量的影响十分重要。由于导引头输出的信号一般采用LVDS或HOTLink格式传输,不能被杂散光测试设备直接接收,设计了一种图像调理卡,采用FPGA为控制核心,将红外探测器输出的图像信号进行格式转换和调理后传输至杂散光测试设备。

关键字:

导引头 LVDS FPGA

JESD204B接口是一个串行解串器链路规范,允许12.5Gbps的最大数据速率传输。使用高级工艺(例如65nm或更小)的转换器支持该最大数据速率,还可提高电源效率。系统设计人员可充分利用该技术相对于低压差分信号(LVDS)DDR的优点

关键字:

数据转换器 JESD204B LVDS PHY模式

lvds介绍

Low-Voltage Differential Signaling 低压差分信号

1994年由美国国家半导体公司提出的一种信号传输模式,它是一种标准

它在提供高数据传输率的同时会有很低的功耗,另外它还有许多其他的优势:

1、低电压电源的兼容性

2、低噪声

3、高噪声抑制能力

4、可靠的信号传输

5、能够集成到系统级IC内

使用LVDS技术的的产品数 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473