LVDS接口电路及设计

LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA(电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE1596.3标准。

本文引用地址:https://www.eepw.com.cn/article/156213.htm1995年11月,以美国国家半导体公司为主推出了ANSI/TIA/EIA-644标准。1996年3月,IEEE公布了IEEE1596.3标准。这两个标准注重于对LVDS接口的电特性、互连与线路端接等方面的规范,对于生产工艺、传输介质和供电电压等则没有明确。LVDS可采用CMOS、GaAs或其他技术实现,其供电电压可以从+5V到+3.3V,甚至更低;其传输介质可以是PCB连线,也可以是特制的电缆。标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps。

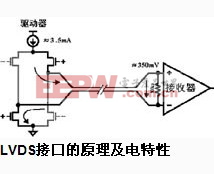

LVDS接口的原理及电特性

一个简单的LVDS传输系统由一个驱动器和一个接收器通过一段差分阻抗为100Ω的导体连接而成,如图1所示。驱动器的电流源(通常为3.5mA)来驱动差分线对,由于接收器的直流输入阻抗很高,驱动器电流大部分直接流过100Ω的终端电阻,从而在接收器输入端产生的信号幅度大约350mV。通过驱动器的开关,改变直接流过电阻的电流的有无,从而产生“1”和“0”的逻辑状态。在有些最新生产的LVDS接收器中,100Ω左右的电阻直接集成在片内输入端上了,如MAXIM公司的MAX9121/9122等。

在LVDS系统中,采用差分方式传送数据,有着比单端传输方式更强的共模噪声抑制能力。道理很简单,因为一对差分线对上的电流方向是相反的,当共模方式的噪声耦合到线对上时,在接收器输入端产生的效果是相互抵消的,因而对信号的影响很小。这样,就可以采用很低的电压摆幅(见表1)来传送信号,从而可以大大提高数据传输速率和降低功耗。

表3是LVDS与其他几种接口的性能比较。同为差分传输接口,LVDS与RS-422、PECL相比,在传输速率、功耗、接收灵敏度和成本等方面都有优越性;与传统的TTL/CMOS接口相比,LVDS在高速、低抖动及对共模特性要求较高的数据传输系统中的应用有着无可比拟的优势。LVDS的低功耗、低误码率、低串扰、低辐射和高速的性能,使得它在激光打印机、蜂窝移动电话基站、网络路由器、数字交叉连接和时钟分配系统等领域的应用日益广泛。

DIY机械键盘相关社区:机械键盘DIY

评论