GaAsSb双异质结双极晶体管集成电路DHBT技术

本文引用地址:http://www.eepw.com.cn/article/155338.htm

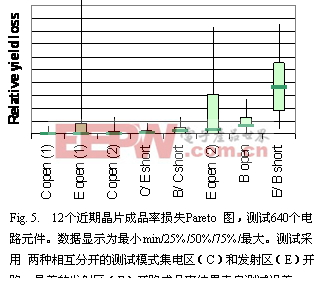

工艺的设计考虑到性能、可靠性和可生产性之间的平衡。从成品率 损失Pareto 图 Fig. 5 中可以看出发射区/基区短路是影响成品率的主要原因,基区电极柱损失是影响远小于发射区/基区短路的第二个原因。影响成品率的其它失效模式的影响相对较小,都在测试不确定范围内。由500个晶体管组成的典型电路所达到的成品率已能够满足小规模仪器的应用应用。

一种新的工艺技术对于Agilent复杂且规模较小的生产其晶片成品率大都如此。造成晶片成品率损失的原因主要有程序错误、晶片破裂、工艺和/或仪器问题。我们的经验显示GaAsSb/InP双异质结双极晶体管DHBTs并不存在异于其它化合物半导体的特有失效机制和更低的可生产性。

评论