基于NIOSⅡ的声纳主机与显控台之间的RS232通信协议

声纳设备一般由换能器(信号转换、收发设备)、信号处理主机(DSP等)和显示控制分机(简称显控台)三部分构成。显控台和主机之间的通信非常重要[1]。

显控台和主机之间的通信距离较远,对通信的可靠性和安全性要求高,但是对通信速度要求不高。所以通信方式可以选择串口通信协议RS232[2]。

显控台上诸多的旋钮、开关以及指示灯、数码管等设备需要丰富的外围接口。这些接口之间具有复杂的逻辑关系。选用FPGA作为显控台主芯片可以满足这些要求。以ALTERA公司的CycloneⅡ开发板为例,其主芯片EP2C8Q208C最多可提供182个用户I/O口,可以满足外围接口要求[3]。在ALTERA公司提供的硬件开发环境Quartus和片上系统开发环境SoPC下,可以非常方便地进行控制模块的开发。也可以构建NIOSⅡ处理器,以及配置NIOS系统自带的硬核,如串口通信模块UART、储存模块Serial Flash等[4]。

本文利用FPGA芯片设计了一套显示控制分机系统,并且以声纳训练靶为应用背景编制了串口通信协议。

1 利用SoPC Builder构建显控台的片上系统

SoPC Builder是ALTERA公司提供的片上系统(SoC)开发工具,它可以配合QuartusII完成FPGA芯片的CPU以及外围设备的配置工作。

1.1 片上系统的构建

在SoPC Builder的开发环境下,选择ALTERA公司开发的32位RISC 处理器NIOSⅡ。标准型的处理器NIOSⅡ/s可以运行在100 MHz的系统时钟下,运算速度超过50 DMIPS[2]。再构建配套的数据存储器SDRAM、程序存储器Serial Flash、系统地址管理器(System ID Peripheral)、编程调试接口(JTAG_UART)以及数码管(SEG)、显示和旋钮(KNOB)、按键(KEYS)等PIO接口。

1.2 RS232 Serial Port的结构

对UART的控制主要通过编程寄存器来实现[2]。根据UART的寄存器结构,在SoPC对应的软件开发环境NIOSⅡIDE下建立C语言的结构体UART_ST,代码如下:

/*--------------UART------------*/

typedef struct

{

union{

struct{

volatile unsigned long int RECEIVE_DATA :8;

volatile unsigned long int NC:24;

}BITS;

volatile unsigned long int WORD;

}RXDATA;

union{

struct{

volatile unsigned long int TRANSMIT_DATA:8;

volatile unsigned long int NC:24;

}BITS;

volatile unsigned long int WORD;

}TXDATA;

union{

struct{

volatile unsigned long int PE:1;

…其他状态寄存器

} BITS;

volatile unsigned long int WORD;

}STATUS;

union{

struct{

volatile unsigned long int IFE:1;

…其他控制寄存器

}BITS;

volatile unsigned long int WORD;

}CONTROL;

union{

struct{

volatile unsigned long int BAUDRATE_DIVISOR:16;

volatile unsigned long int NC:16;

}BITS;

volatile unsigned int WORD;

}DIVISOR;

}UART_ST;

2 显控台与主机之间的通信

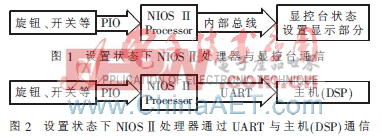

声纳设备有两种工作状态——设置和工作。在这两种状态下,显控台与主机的通信方式有三种,分别如图1~3所示。

评论