基于NiosII的I2C总线接口的实现

为了保护NiosⅡ嵌入式系统的运行现场,在掉电之前,需要把系统的重要数据保存在非易失存贮器中。针对这种保存的数据量不大特点,本文提出采用NiosⅡ+AT24C02设计方案,在介绍AT24C02A芯片主要特性和分析I2C通信协议原理基础上,重点介绍Nios Ⅱ与AT24C02A之间接口电路的设计方法,包括接口电路的寄存器定义、逻辑功能模块设计和驱动程序的编写三个方而的内容,利用嵌入式逻辑分析仪(SigalTap Ⅱ Logic Analyzer)来分析接口信号时序,分析结果表,本接口所产生的读写时序满足I2C的通信协议要求,验证了设计的正确性。

本文引用地址:https://www.eepw.com.cn/article/149910.htm1 AT24C02A芯片简介

AT24C02A芯片,是由ATMEL公司生产的基于I2C总线型的串行电可擦除的可编程存储器(EEPROM),内部含有2Kbit的存储单元,是通过二根线(SDL与SCL)与外部I2C控制器交换数据。

AT24C02A芯片的主要特性如下:

低电压和标准电压操作

-2.7(VCC=2.7V至5.5V)

-1.8(VCC=1.8V至5.5V)

片内存储容量为256×8 bit(2K)

2线串行接口

施密特触发器,过滤输入的噪声抑制

双向数据传输协议

100 kHz(1.8V、2.5V、2.7V)和400 kHz(5V)兼容性

写保护引脚的硬件数据保护。

2 I2C通信协议

2.1 I2C通信协议简介

AT24C02A器件采用成本低廉的I2C(Inter integrat-ed Circuit)总线通信协议,SDA和SCL均为双向I/O线,通过上拉电阻接正电源。当总线空闲时,两根线都是高电平。连接总线的器件的输出级必须是集电极或漏极开路的。I2C总线的数据传送速率在标准工作方式下为100kbit/s,在快速方式下,最高传送速率可达400kbit/s。

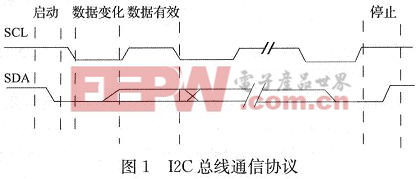

在数据传送过程中,必须确认数据传送的开始和结束信号(也称启动和停止信号)。当时钟线SCL为高电平时,数据线SDA由高电平跳变为低电平则定义为开始信号;当SCL为高电平时,SDA由低电平跳变为高电平则定义为结束信号。开始和结束信号都由主器件产生。在开始信号以后, 总线即被认为处于忙状态;在结束信号以后的一段时间内,总线被认为是空闲状态。

在I2C总线开始信号后,依次送出器件地址和数据,I2C总线上每次传送的数据字节数不限,但每一个字节必须为8位,而且每个传送的字节后面必须跟一个认可位(第9位),也叫应答位(ACK)。从器件的响应信号结束后,SDA线返回高电平,进入下一个传送周期。

2.2 AT24C02A器件读写时序

一个写功能要求一个8位数据字地址随设备地址字和acknowledgement(承认)。在这个地址的收据之上,EEPROM将再响应由一个0且时钟在第一个8位数据字。随着8位数据字的收据,EEPROM将输出一个0且寻址设备,例如一个微控制器,必须指定带停止条件的写时序。在这个时间EEPROM进入一个internally-timed(内部定时)写时序,tWR,对于非易失性内存。所有输入关闭在这个鞋周期之间且EEPROM将不响应直到写完成(关系Figure 2)。

读功能被初始化与写功能相同由外部的读/写选择位在设备地址字被设置为1。有三个读功能:当前地址读取,随机地址读取和顺序读取。

当前地址读取:内部数据字地址计数器包含最后一个地址访问在最后一个读或写功能期间,以1递增。这个地址保持有效在芯片电源提供工作期间。地址“折返”在读来自于最后内存页到第一页的第一个字节期间。这个地址“折返”在写来自于当前页的最后一个字节到同样页的第一个字节期间。

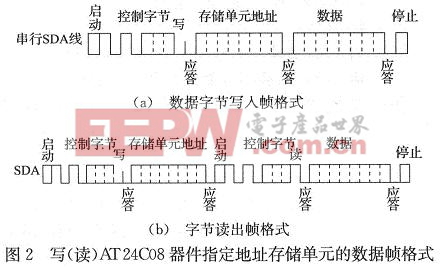

图2为写(读)AT24C02A器件中指定地址存储单元的数据帧格式,图2(a)为写操作的帧格式,(b)为读操作帧格式。要想把一个字节数据发送到器件中(或从器件中读取一个字节数据)除了给出具体的地址信息之外,还要给出该器件的控制信息:首先由控制器发出“启动”信号,启动I2C总线的通信,然后发送一个控制字节,前7位为器件的片选地址,最后1位为读写控制位,“0”表示写,“1”表示读。当传完控制字节之后,挂在I2C总线的所有的器件比较控制字节片选地址(前7位)是否与自已的物理地址一致,如一致,则发一个应答信号。控制器接收到应答信号之后,再发器件内部存储单元地址和其他的信息。

3 AT24C02A读写控制接口设计

3.1 寄存器组定义

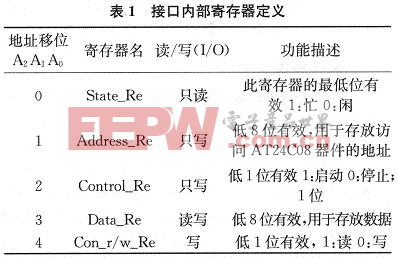

为了实现NiosⅡI能与外部设备进行交换数据,首先要在AT24C08读写控制接口中定义寄存器,包括数据寄存器、状态寄存器和控制寄存器。表4-1AT24C02A读写控制器内部寄存器定义的情况:STate_Re为此接口电路的状态寄存器,最低位有效,用来表示接口电路的状态,“1”表示接口处于“忙”状态中,此时表示接口正处于读写外部设备(AT24C02A)中,不能对此控制接口进行操作,只到接口处于“0”状态时为止;Address_Re为数据寄存器,用于存放NiosⅡ要访问AT24C02A器件内部单元的地址数据;CONtrol_Re为控制寄存器,控制着接口电路启动或停止,“1”为启动,“0”停止;Data_Re为数据寄存器,用于存放传输的数据;Con_r/w_Re为控制寄存器,控制数据的传输方向,高电平为读(输入),低电平为写(输出)。

3.2 逻辑功能模块设计

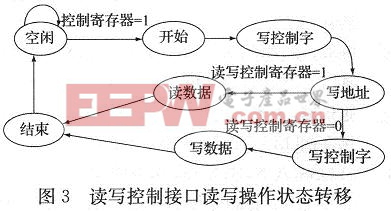

在接口电路中,除了定义接口电路的寄存器组之外,还要利用硬件描述语言来描述接口电路要实现的功能,即逻辑功能模块的设计。接口电路要完成的主要功能是,用接口电路产生如图3所示的时序,成功读写外部存储器件。在本设计中,采用了有限状态机来实现这一功能,图3为本设计的各个状态之间转换状态图:当NiosⅡ要交换数据时,首先要读State_Re的值,并判定电路是否为“空闲”状态,只有状态机处在空闲状态,才允许进行一次读写操作,并修改状态寄存器的值为“忙”状态;当完成一次读写操作时,修改状态寄存器的值为“闲”状态。

4 在NiosⅡIDE环境中软件设计

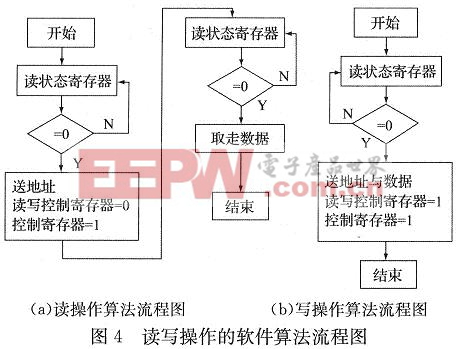

打开NiosⅡEDS,并点击new菜单建立工程文件,在IDE环境中完成接口电路驱动程序编写。驱动程序主要的任务,是判断接口电路所处的状态,当接口电路处于“闲”状态时,设置好接口电路中的寄存器中的值,并启动一次读写操作。图4为驱动程序的算法流程图。

5 测试结果

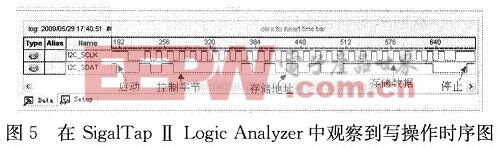

为了验证设计的正确性,对以上设计进行测试。在测试的过程中,可以利用嵌入式逻辑分析仪(SigalTapⅡLogic Analyzer)来分析信号时序,打开工程文件,点击File菜单,为本设计新建一个矢量波形文件(Vectorwaveform File),把要测试的信号添加到此文件中来,并设置好相关参数,保存并编译系统,然后把系统的配制文件下载到EP1C6Q240C8可编程器件中等待调试,最后,在:NiosⅡ的ID E中,把驱动程序下载到可编程器件中,并在QuartusⅡ软件中打开矢量波形文件,观察被测信号的时序,图5为接口电路把数据为“11111111”写到地址为“10101010”单元中的时序图。从图可以看出,启动时序、数据传输时序和停止时序都满足I2C通信协议要求,验证了本接口电路的正确性。

6 结束语

本文在讨论了I2C通信协议的基础上,重点介绍了AT24C02A读写接口电路设计方法,包括接口电路的寄存器定义、逻辑功能模块设计和驱动程序的编写,并利用嵌入式逻辑分析仪(SigalTapⅡLogic Analyzer)对本接口电路进行测试,测试结果表明,本设计满足设计要求,并在实际电路中得到应用。

评论