应用高带宽示波器表征 GDDR5 数据抖动,确保有效的数据传输

GDDR5(Graphics Double Data Rate,图形双倍数据速率存储接口,第 5 版)动态随机存取图形卡存储技术已应用于主流移动和游戏用户的高性能 GPU(图形处理器)。最新的 GDDR5 技术可提供 5Gb/s 或更高的数据速率。高数据速率条件下,数据抖动测量是了解抖动对数据有效窗口影响的重要手段。测量并了解抖动分量可以让设计人员尽可能减少整个系统设计的抖动,以确保有效且精确的数据传输。需要分离读和写操作从而分别进行数据有效窗口分析。GDDR5 的设计包括自由运行的数据时钟(WCK)、很小的数据单位间隔以及非常小的读/写数据与WCK之间可分辨时间偏移,因此识别读/写数据以进行数据抖动测量十分困难且耗时。高带宽示波器或混合信号示波器是两类常用的数据抖动测量设备。本文将介绍仅使用高带宽示波器 4 个通道的新型 GDDR5 数据抖动测量技术。

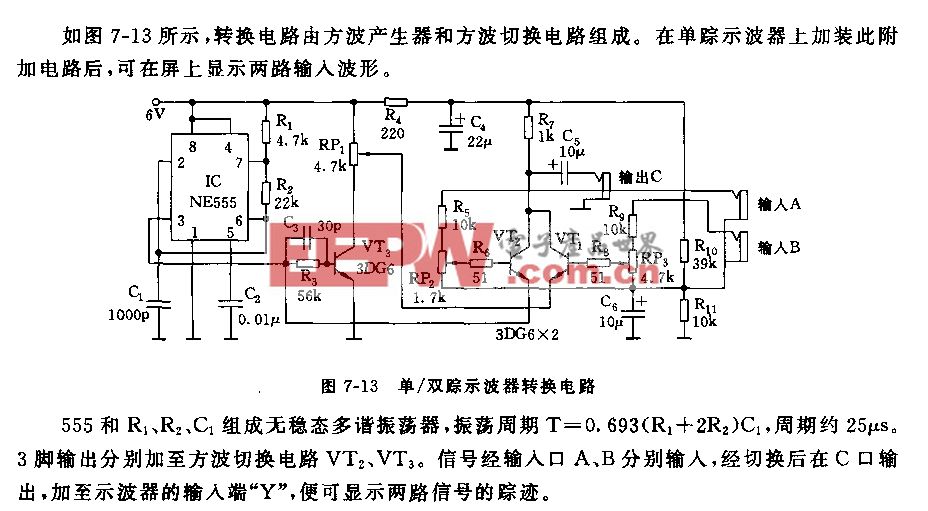

本文引用地址:https://www.eepw.com.cn/article/142457.htm抖动对 GDDR5 数据的影响

GDDR5 SGRAM 传输数据使用自由运行差分前向时钟(WCK/WCK#),并在前向 WCK 的两个边沿上分别寄存并驱动输入和输出数据,以用于读和写训练。读/写训练支持数据定时和幅度电平裕量优化。尽管 JEDEC 标准没有相关规定,普遍观点认为表征抖动特性是在如此高的数据速率传输条件下的重要测量任务。导致 GDDR5 系统产生抖动的原因,例如码间干扰(ISI)、串扰、占空比失真(DCD)等,这些都会限制图形卡以及存储器控制器与 DRAM 接口的性能。

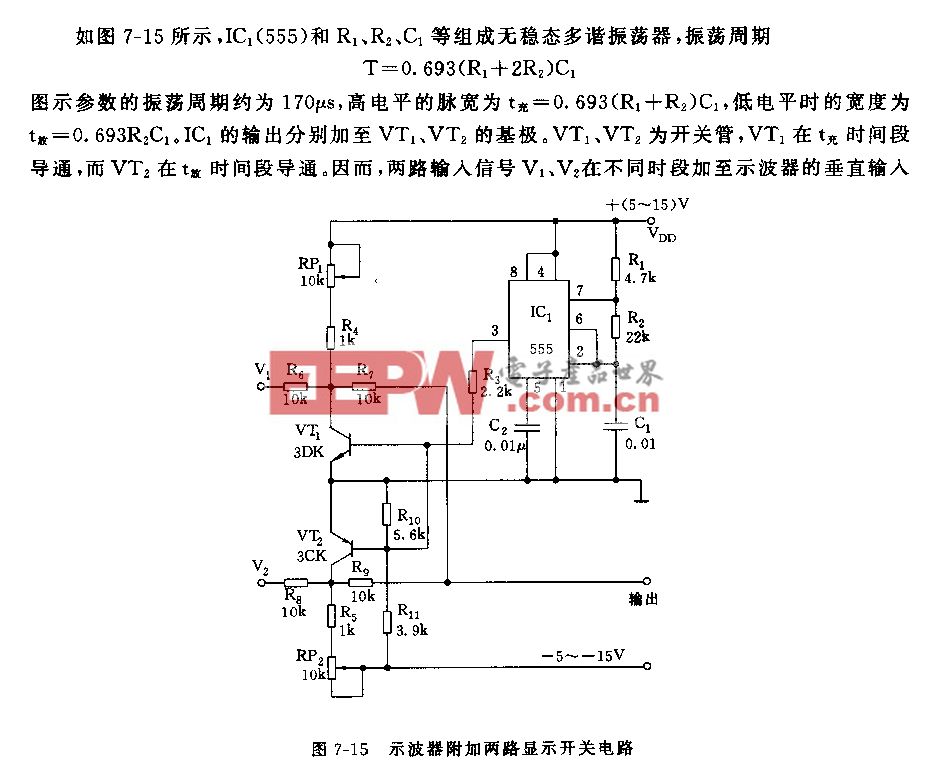

抖动是指信号跳变边沿与理想时间的偏差。随着数据速率的提升,定时裕量日趋严格,甚至每一皮秒的裕量都变得更为重要。高数据速率时代,微小的抖动都可能导致读写数据的数据有效窗口关闭,最终增加比特误码率和数据采样误差。

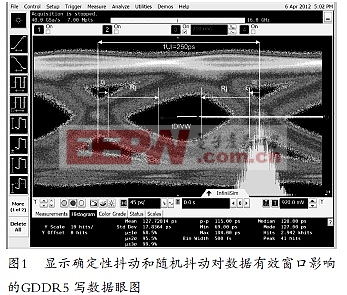

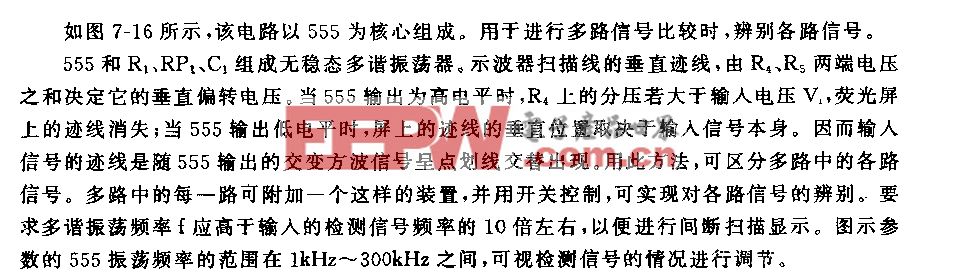

在高数据速率(例如 5 Gb/s 或以上)条件下,数据有效窗口非常小。系统中的噪声或相邻电信号的串扰甚至电磁干扰都极易造成信号失真和信号完整性问题,导致数据采样误差。实时眼图可以提供眼图高度和眼图宽度测量以检查信号完整性并预估数据有效窗口。但是,仅使用实时眼图测量数据眼图无法获得完整的有效数据窗口分析和比特故障率预测。图 1 是一个具有一百万单位间隔(测得的单位间隔)的写数据眼图。一百万单位间隔的初始测量得到 200ps 的数据输入有效窗口。确定性抖动(DJ)线和随机抖动(RJ)线显示了长时间累积的抖动效应和实际数据输入有效窗口,即一万亿单位间隔(1e-12 比特误码率或 BER)后的 tDIVW(数据输入有效窗口)。确定性抖动通常有界、可预测并且与数据码流相关联,例如码间干扰和占空比失真。随机抖动通常为高斯抖动且无界。同其它高斯分布一样,该分布的峰峰值将随着数量的增加而增大。因此,总体抖动是随机抖动乘以BER 倍数因子再加上确定性抖动。注意,图示是写数据的数据输入有效窗口。您可以发现,抖动 BER 测量计算非常重要,是总抖动统计测量的重要组成部分,可以帮助您了解设计的数据有效窗口结果并预测设计中的错误率。另外,了解抖动分量和抖动源可支持设计人员降低设计抖动,确保更精确的数据传输。

评论