Zynq-7000可扩展处理平台新闻背景

关于最新可扩展处理平台您首先想问的或许就是‘Zynq’这个名称究竟是什么意思。这个词很容易让人联想到 zinc,也就是电池、日光屏、合金制品和药品中最常见的化学元素锌。锌与其他金属的合金可实现增强型功能,根据合金的不同对象表现为不同的色彩。锌最常见的用途就是电镀。

本文引用地址:https://www.eepw.com.cn/article/127580.htm那么这个名称与电镀之间有什么联系?

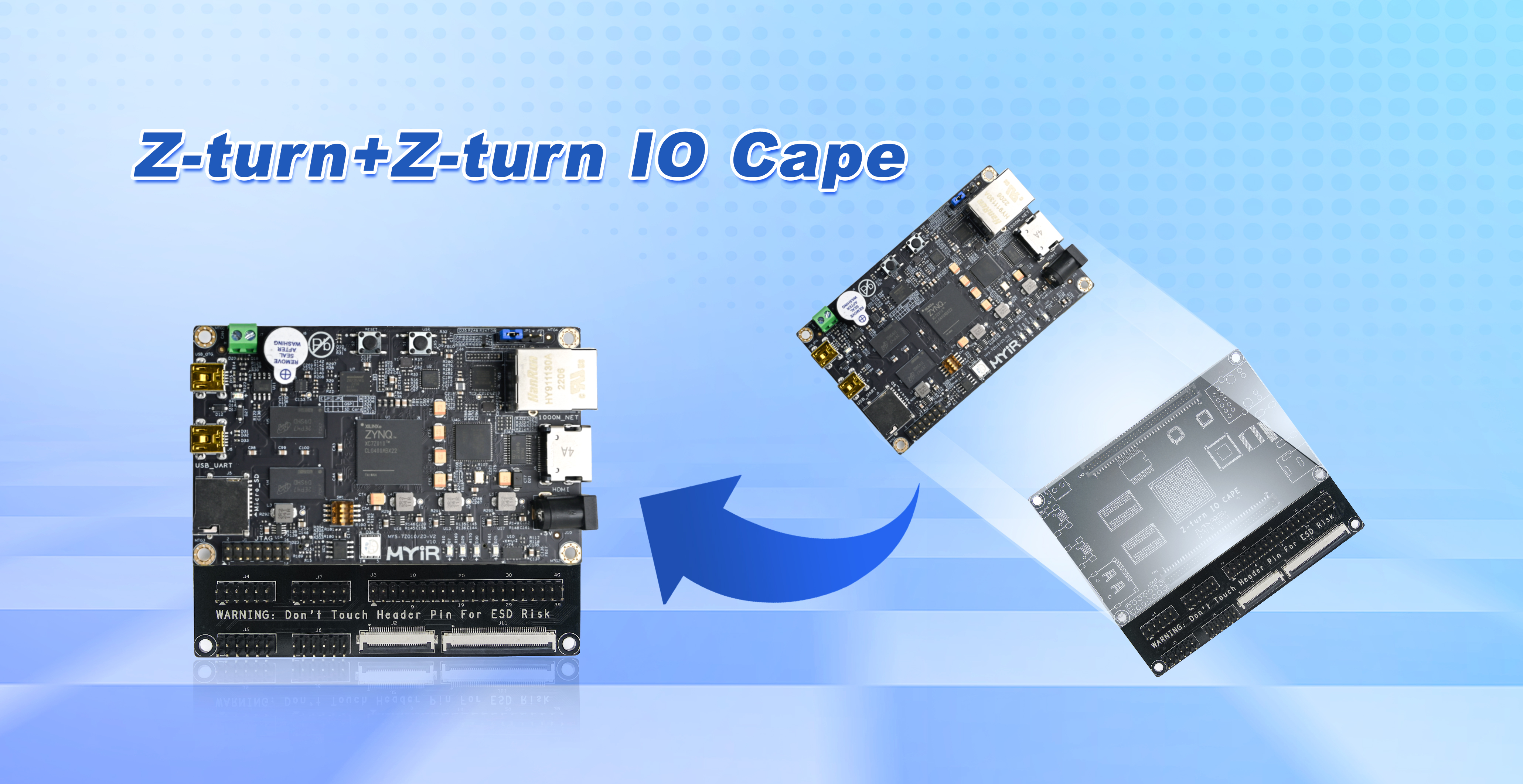

在 2010 年 4 月硅谷举行的嵌入式系统大会上,赛灵思发布了可扩展处理平台的架构详情,这款基于无处不在的ARM 处理器的 SoC可满足复杂嵌入式系统的高性能、低功耗和多核处理能力要求。赛灵思可扩展处理平台芯片硬件的核心本质就是将通用基础双 ARM Cortex-A9 MPCore 处理器系统作为“主系统”,结合低功耗 28nm工艺技术,以实现高度的灵活性、强大的配置功能和高性能。由于该新型器件的可编程逻辑部分基于赛灵思 28nm 7 系列 FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列 FPGA 的一致性,同时也方便日后本系列新产品的命名。

除了芯片外,赛灵思 Zynq™-7000 系列还构成了最终平台产品的基础。赛灵思联盟计划生态系统和 ARM互联社区的成员提供的软件开发与硬件设计实现工具、广泛采用的操作系统、调试器、IP及其他元素的工具就好像“电镀”在一起一样,从而使可扩展处理平台成为了可能。

以处理器为中心的开发流程

Zynq-7000 可扩展处理平台采用熟悉的工具流程,使嵌入式软/硬件工程师能以类似于赛灵思 ISE 设计套件和第三方工具提供的嵌入式设计方法,执行各自的开发、调试和实现工作。

软件应用工程师可使用与此前设计相同的 ARM 开发工具。赛灵思为嵌入式软件应用项目提供了软件开发套件(SDK),一种基于 Eclipse 的工具套件。ARM Development Studio 5 (DS-5) 和ARM RealView 开发套件 (RVDS™)等其他第三方开发环境也可使用。处理子系统可独立于可编程逻辑结构加电启动。

应用软件工程师可从一系列预配置处理器系统启动代码中进行选择,满足单处理器、非对称多处理器 (AMP) 或对称多处理器 (SMP) CPU 拓扑要求。这种预配置的启动代码作为实例启动代码,可就选定的拓扑采用适当的外设、驱动程序和API,满足特定评估板的要求。这就让软件工程师无需依靠任何硬件或固件工程师就能启动设计工作。

为了让软件应用跟上硬件设计的步伐,固件工程师可采用ISE 设计套件嵌入式版本的新功能:处理器配置工具 (PCT)。PCT 能以图形化形式帮助您配置处理子系统中的系统级寄存器和外设寄存器。配置后,配合启动代码使用的 PCT 输出配置文件可创建定制启动环境。随后即可用 SDK 编译和调试开发板支持包。

硬件设计流程类似于 ISE 设计套件中的嵌入式处理器设计流程,不过可扩展处理平台新增了一些步骤。处理子系统是一个带有众多通用外设的完整双处理器系统。硬件设计人员可在可编程逻辑中为处理子系统添加更多外设,从而提高处理能力。硬件开发工具 Xilinx Platform Studio 实现了大部分一般硬件开发步骤的自动化。PCT 还能用于帮助设计人员优化器件管脚。

1 个处理系统,4 款器件

Zynq-7000系列中的 4 款产品具有完全相同的 ARM 处理系统,但是可编程逻辑资源的可扩展性有所不同, 因而适用于不同的应用。

Cortex-A9 多处理器内核(MPCore) 由2 个 CPU 组成。每个 CPU 都是一个 Cortex A9 处理器,带有专门的 NEON 协处理器(媒体和信号处理架构,增加了面向音频、视频、3D 图形、影像和语言处理的指令)和双精度浮点单元。Cortex-A9 处理器是一款带有 L1 高速缓存子系统的高性能低功耗 ARM 宏单元,提供了全面的虚拟存储器功能。该处理器采用 ARMv7架构,运行 32 位 ARM 指令、16 位和 32 位 Thumb 指令以及 Jazelle 状态 8位 Java 字节码。此外,处理系统包括Snoop Control Unit、L2 缓存控制器、片上 SRAM、定时器/计数器、DMA、系统控制寄存器、器件配置和 ARM CoreSight™ 系统。就调试而言,其包含了嵌入式跟踪缓冲器 (ETB)、指令跟踪宏单元 (ITM) 和 ARM 提供的Cross Trigger module (CTI)。除了上述之外,它还包含了赛灵思提供的AXI Monitor (AXIM) 和 Fabric Trace (FTM) 模块。

Zynq-7030 和 Zynq-7040 这两个较大的器件均具备高速低功耗的串行连接功能,其内置的千兆位级收发器运行速度高达 10.3125 Gbps。这两款产品分别提供相当约 190 万和 350 万个 ASIC 门(即 125,000和 235,000 个逻辑单元),DSP 峰值性能分别达 480 GMAC 和 912 GMAC。Zynq-7010 和 Zynq-7020 这两款较小的器件分别提供约 43 万和 130 万个 ASIC 门(即 30,000和85,000 个逻辑单元),DSP 峰值性能分别为 58 GMAC 和 158 GMAC。

每款器件包含一个通用模数转换器 (XADC) 接口,而该接口又包含 2 个 12 位 1 Msps ADC以及多个片上传感器和外部模拟输入通道。XADC比前代 Virtex® FPGA 的系统监控器具有增强型功能。两个 12 位 ADC 支持的采样率高达每秒 100 万次,而且能对多达 17 个外部输入模拟通道进行采样。ADC 支持丰富的应用,能满足这些应用在带宽不到500 KHz条件下处理模拟信号的要求。

可编程逻辑可由用户配置,并通过“互连”模块连接在一起,从而可提供用户定义的任意功能,以扩展处理器系统的性能和功能。一系列互连模块相互配合,可根据应用需求在逻辑模块间路由信号。赛灵思可编程逻辑软件工具可将 RTL 应用编译到位文件中,然后将该文件载入可编程逻辑中用以配置可编程逻辑的功能。应用可以载入单个静态可编程逻辑配置也可以根据应用需要动态选择配置。我们也可以通过部分重配置功能对可编程逻辑的选定区域进行配置。

器件两个区域的互连操作对用户而言大部分都是透明的。主/从设备之间的存取根据地址范围通过 AXI 互连机制路由,也就是说,每个从设备要分配一个地址范围。多个主设备可同时访问多个从设备,每个 AXI 互连机制采用两级仲裁方案来解决冲突。

处理系统与可编程逻辑紧密集成,内部互连达 3000 多个,带宽相当于约100Gb,为系统架构师提供了一款具有高带宽和低延迟接口的处理平台,从而为高强度计算应用带来了前所未有的软硬件分区优化。举例来说,工业市场需要小型化灵活分区、高性能低成本生态系统支持来实现工业控制系统的成功开发与实施。基于双 Cortex-A9 MPCore 的处理系统配合可编程逻辑的并行处理能力为目前的工厂自动化和视觉系统带来了确定性性能所必需的计算能力。在汽车市场领域,防撞系统的图形处理和识别技术需要能在确保低系统功耗与成本、高集成度的基础上实现大幅 DSP 加速的单芯片平台。基于双 Cortex-A9 MPCore 的处理系统配合可编程逻辑的强大并行处理能力可为图形处理和高级分析功能提供其所需的计算能力,从而满足汽车及其他市场对智能系统的需求。

总结

ARM 双核 Cortex-A9 MPCore 处理器和赛灵思 28nm 可编程逻辑的紧密集成,为高端嵌入式系统提供了强大的串行和并行处理能力。利用软/硬件设计与实现的统一设计流程,嵌入式设计团队能在他们熟悉的设计环境中开展工作,从而实现工作效率的最大化。不过,Zynq-7000 可扩展处理平台系列的最大优势还在于客户能以较低的总拥有成本构建定制解决方案,满足其独特的需求并实现产品差异化。

评论