一种多体制通信时间同步算法及其FPGA实现

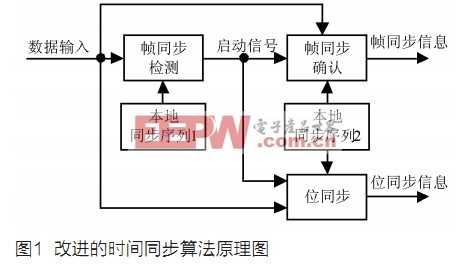

帧同步确认

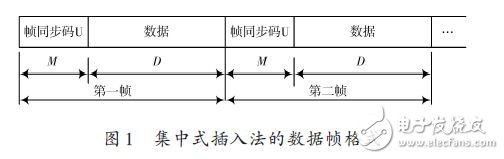

本文引用地址:http://www.eepw.com.cn/article/116957.htm帧同步确认的主要目的是判断帧同步检测结果是否属于假同步,减少出现假同步的概率。它利用接收同步序列的后半部分与本地同步序列的后半部分(即图1中的本地同步序列2)之间的相关性实现。由于帧同步确认时,位同步、载波同步等模块同时工作,帧同步确认受载波频偏等因素的影响较小,可以采用接收序列与本地序列直接相关的算法实现。

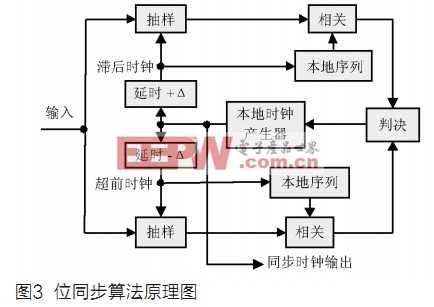

位同步

位同步模块在帧同步检测成功后启动(与帧同步确认同时进行),利用接收同步序列的后半部分与本地同步序列的后半部分(即图1中的本地同步序列2)之间相关性,通过利用比较时钟与接收码元之间的相关差来判断本地时钟是否需要进行调整,从而实现位同步。当最佳判决点处于接收信号码元的中间位置时,位同步算法原理如图4示,其中超前时钟和滞后时钟作为比较时钟。对于最佳判决点不处于码元中间的情况,只要修改图3中超前、滞后时钟与本地时钟之间的相位差即可。

相关器采用与帧同步检测相同的相关方法式(1):当最佳判决点处于码元中间的情况,即本地时钟相位与最佳判决点一致时,超前时钟和滞后时钟相位都在最佳判决点附近,其相关结果基本相同,本地时钟产生器不需要进行调整;当本地时钟相位超前于最佳判决点时,超前时钟远离最佳判决点,其控制下相关器的输出减小为(P1-1)/2,而滞后时钟控制下相关器的输出仍为(P1-1),判决模块通知本地时钟产生器进行滞后处理。同理,当本地时钟相位滞后于最佳判决点时,产生器进行超前处理。

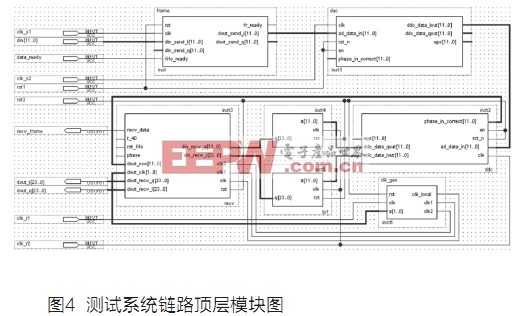

FPGA实现与仿真验证

根据新一代无线通信统一平台的特点,同步功能需要在FPGA内实现。本文利用Altera的quartus设计软件,采用自顶向下的模块化设计方法,用VHDL语言完成时间同步相关的各个模块的编程设计,并利用仿真软件modelsim完成仿真验证。测试系统如图5。其中,发端主要包括成帧(frame)和上变频(duc)两个模块,将信源数据按一定标准组成帧,并调制到一定的中心频率发出;收端主要包括下变频(ddc)、低通滤波(lpf)、时钟生成(clk_gen)和同步处理(recv)等模块。其中,recv包含了帧同步、位同步和载波同步等模块,duc和ddc模块为了测试存在载波频偏时的同步算法性能而加入。

评论