SPARQ系列述评之二

摘要:随着半导体工艺的不断发展,数字信号的速率也愈来愈高,Gbps以上的高速信号已经随处可见。面对高速设计的新领域,硬件设计工程师们需要改变传统的设计理念,他们需要以更加超前的思维去思考自己将要设计的信号的质量,或许在制定产品设计方案的时候就需要进行调研;需要在设计过程的每一个环节去思考信号质量问题,如方案设计环节,原理图设计环节,PCB设计环节,测试验证环节等等;需要考虑到系统中的每一个构成成分可能给信号质量带来的影响,如过孔,电容,电感,阻抗,接插件等等;所有高速设计相关的问题也常被统称为信号完整性(即SI,Signal Integrity)问题,SI是当前硬件设计工程师们的一个最热门的话题之一。和SI相关的两个最为重要的工作是信号完整性仿真和信号完整性测试。信号完整性仿真是指使用仿真软件将芯片、信号传输链路的模型连接到一起,进行初步的信号质量的预测,信号完整性仿真中一个最为重要的模型是S参数模型,它常被用来模拟传输线、过孔、接插件等的模型,在仿真之初S参数常常是通过电磁场仿真软件等仿真的方法获得,然后再用相应的测试仪器如TDR、VNA以及力科新推出的新型专用于信号完整性领域的信号完整性网络分析仪SPARQ等进行测试验证。S参数模型贯穿于整个信号完整性分析过程,它是一切信号完整性问题的心脏。

本文引用地址:https://www.eepw.com.cn/article/113844.htm关键词: 信号完整性 仿真 S参数 建立时间 保持时间

一、信号完整性的基本概念

SI(Signal Integrity)是指传输系统在信号的传输过程中保持信号的时域和频域特性的能力。

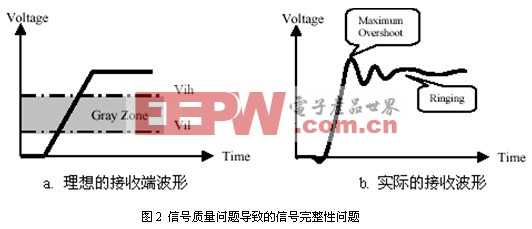

在理想情况下,信号在传输过程中不应该发生任何的变化,但是真正理想的传输通道是不存在的,实际情况是信号经过一个非理想的传输通道后会发生各种各样的信号完整性问题。从信号质量角度考虑,主要有过冲、下冲、振铃、反射等,信号质量问题会导致接收端芯片错误的判别接收到的信号的逻辑特性,如将0电平误认为是1电平,从而出现数据传输错误,另外一方面是时序问题,主要表现为数据和时钟之间的时序关系,如接收端的时钟信号和数据信号不满足建立时间和保持时间。

概括来说,信号完整性问题主要表现为两个方面,一是信号质量问题;二是时序问题(主要是建立时间和保持时间)。

1、信号质量问题

评论