基于BQ40z80的电量计电路设计原则

作者:Weng Iris

1.介绍

BQ40z80是完全集成的2-7节锂离子或锂聚合物电池管理芯片,采用已获专利的Impedance Track™技术,具备电流、电压和温度等全面的可编程保护功能。其硬件电路设计主要分为三个部分:主电流回路模块、电量计模块和保护模块。

2.主电流回路

主电流回路即指在电量计的控制下对电池进行充电、放电的电流回路。当充电时,该回路的电流从PACK+开始,经过用于控制充电和放电的开关FETs、化学保险丝、电池和电流采样电阻,最终回到PACK-。

2.1充、放电FETs

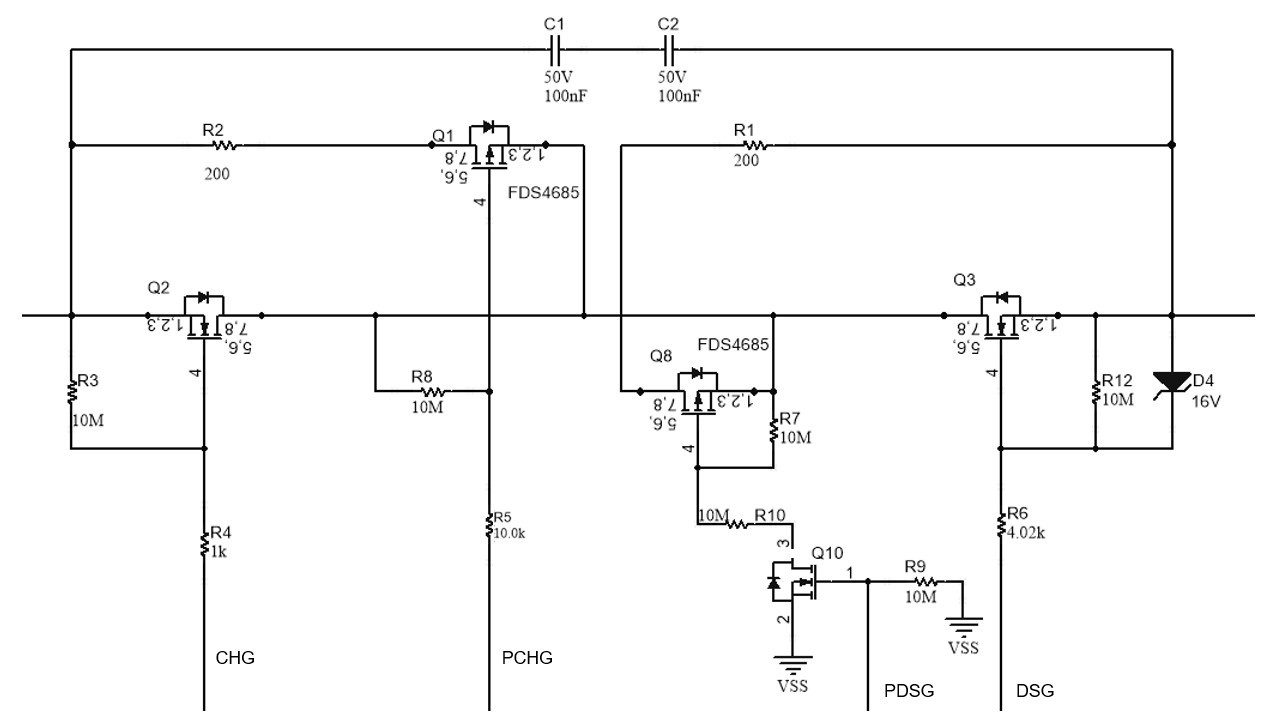

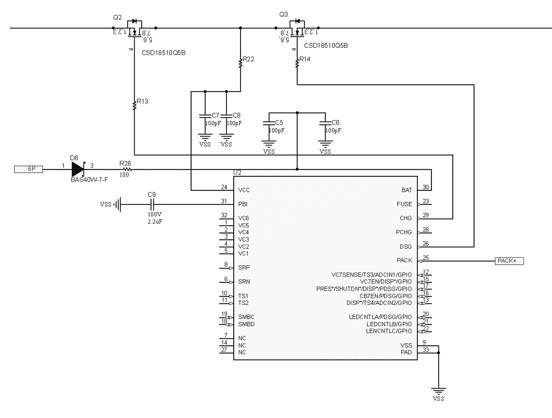

充、放电的两个N-CH FETs以漏极对接的方式串联在PACK+和电池组的正极,如图2-1所示,Q2、Q3分别是充、放电FET。当进行充电或放电时,Q2和Q3同时导通;当充电停止时,Q2关断;当放电停止时,Q3关断。

图2-1 充、放、预充、预放电MOSFET电路图

在进行FETs选型时应注意以下两点:(1)FET的额定电压值必须大于电池的最大电压;(2)考虑到放电时负载端产生反电动势的情况,放电FET的额定电压值应比充电FET稍大。

其驱动信号CHG和DSG上的栅极驱动电阻典型值分别为1kΩ和4.02kΩ,该阻值不同是由引脚内部结构决定的,使FETs的开通时间在几毫秒左右;FETs栅源间电阻典型值为10MΩ, 以确保栅极开路时FETs关断,避免误导通现象。

跨接在FTEs两端的电容C1、C2起到在ESD事件中保护FETs的作用,其两端路径应本着尽可能短和宽的设计原则,同时还应注意C1和C2的额定电压都应比系统相应最大电压更大,从而达到在某一个短路时另一个仍能起到保护作用的效果。

2.2预充、预放电FETs

预充电功能指当电池因过度放电、放置过久的自放电等原因导致两端电压过低时,若直接进入正常充电模式易损坏电池或影响电池使用寿命,此时需使用预充电功能,以小电流将电池充电至正常电压范围内后再转换为正常充电模式。它通过对P-FET的控制实现,预充电流的大小通过限流电阻R2=(VCHARGER-VBAT)/R2设定,同时兼顾对电阻上的热量消耗P=(VCHARGER-VBAT)2/R2的考虑。

预放电功能是指当电池应用于较大的电容负载时,启动瞬间易产生瞬间冲击电流,需先以软起的形式进行缓慢充电,从而减小瞬间大电流。如图1-1所示,来自Pins 16、17或20的驱动信号提供一个高电平使N-CH FET Q10导通,从而将预充电P-CH FET Q8的栅极接入地,使Q8导通,预充电回路打开,其预放电速率由限流电路设定。

2.3 防反接保护

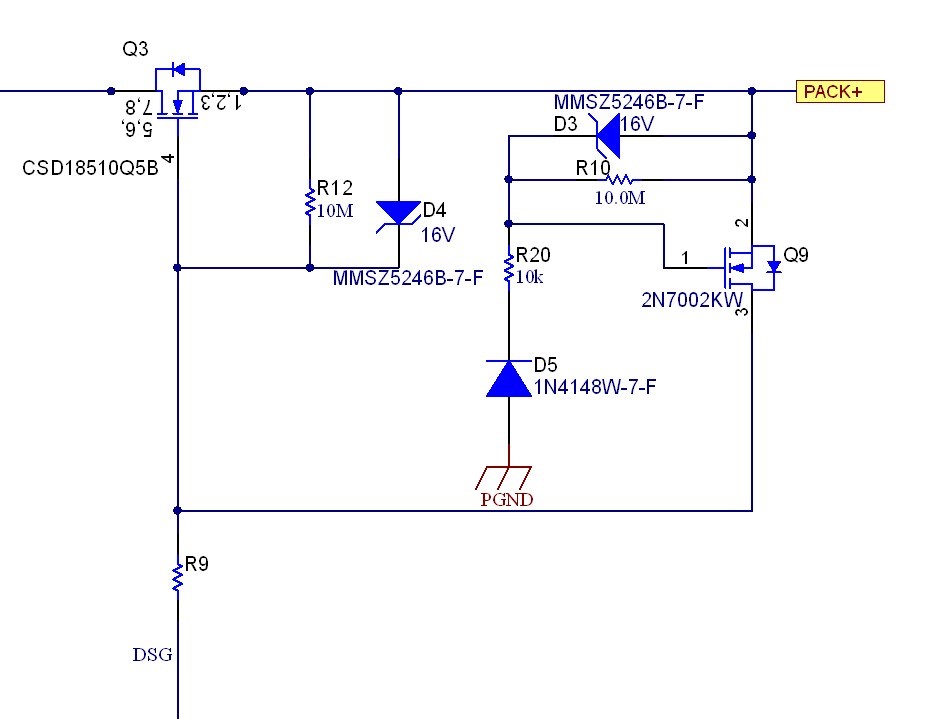

充电器反接会对系统造成极大伤害,因此需为此设计相应的保护电路,如图2-2所示。

图2-2 反接保护电路

若无此保护,当PACK+上出现一个略小的负信号,放电FET将进入线性工作区,影响电路正常工作。但加入防反接电路后,PACK+上的负信号会使栅极接地的N-FET Q9导通,使放电FET的栅源极短路,从而起到保护作用。在选型时应选择具有较低Vgs(th)的N-FET,已达到可靠及时的保护效果。

2.4电芯输入

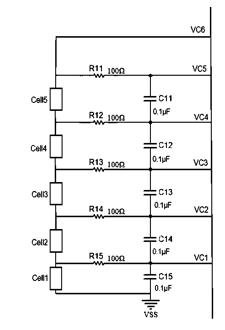

BQ40z80可以实现2-7节锂电池的管理和保护。对于2-6节的电池,芯片内部包含已集成的电压均衡模块,只需正常进行连接,未使用的Pins短接处理,例如图2-3所示在5节串联电池的应用中需将VC6与VC5短接。同时,每节电芯的输入应设计一个RC滤波电路,在起到ESD保护作用的同时,也可实现对输入电压信号实现初步滤波。考虑到该电阻处在电压均衡回路上,阻值选取应在内部电压均衡和滤波频率间进行均衡。

图2-3 5节电芯输入连接方式

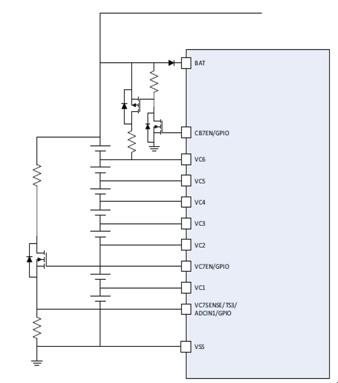

对于7节电芯的电池则需进行额外的设置将电压均衡设置在外部,其连接方式如图2-4所示,其中,Pin VC7EN使能对7P的电压测量。

图2-4 7节电芯连接方式及其外部电压均衡模块

2.5电流采样电阻

通过由采样电阻所确定的回路电流值及方向是电量计的重要输入信号。BQ40z80内部有一个用于电流检测的集成Delt-sigma ADC,可实现的测量范围是-0.1V到0.1V。通过Pins SRP、SRN检测到的采样电阻两端的压降判断流经电池的电流,一方面用于判断系统处于充电还是放电模式,当检测到VSR=V(SRP)-V(SRN)为正值时,系统处于充电状态,反之处于放电状态;另一方面通过库伦计得到的积累电荷是电量计算的关键参数之一。

BQ40z80推荐的采样电阻阻值为1mΩ-3mΩ。对于大电流的应用场合,在确保可靠的开尔文连接的前提下支持并联采样电阻的方案。为防止短路情况下的大电流使电阻两端电压值超过Pins SRP、SRN的最大绝对输入值0.3V,两个100Ω的电阻R36、R37应串联接入采样信号。

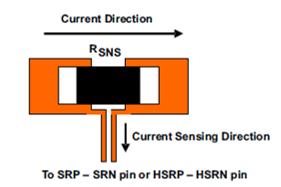

图2-5 采样电阻开尔文连接

综上,如何确保较高的测量精度是设计采样电阻时的关键。应注意以下三点:(1)连接方式应选择开尔文连接,如2-5图所示;(2)电阻选型应注意使其温漂小于50ppm,以减小因温度变化引起的测量电流的漂移;(3)设计合适的滤波电路以减小噪声干扰,详见3.1节。

3.电量计

3.1库伦计接口

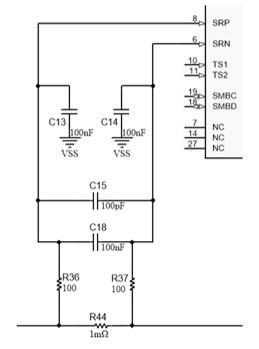

为了提高采样电流精度,除了对采样电阻的处理还可对输入信号的接口电路进行设计,如图3-1所示是为减小信号噪声而对采样信号设计的低通滤波电路。

图3-1 库伦计接口低通滤波电路

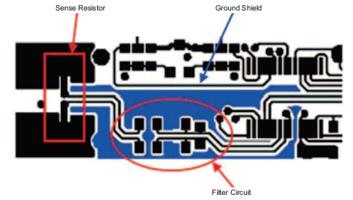

Pins SRP、SRN两端分别设置0.1μF的滤波电容C13和C14,以实现对100k-100MHz频率范围内的噪声的滤除作用,中间跨接的两个100pF和0.1μF的电容用于滤除高于100MHz的噪声。以上所有滤波元件都应放置在离输入端尽量近的地方,且采样电阻两端信号到滤波电路的路径应保持平行,最后,在滤波电路周围铺满地平面会对更良好的滤波效果有所帮助,如图3-2所示。

图3-2 库伦计接口滤波电路Layout方式

3.2电源管理

BQ40z80的供电系统包括三部分:来自电池的BAT、来自充电器的VCC和内部进行瞬间供电的PBI,据工作状态的不同对电源供应进行管理,如图3-3所示。

图3-3 BQ40z80供电管理系统

通常,由电池对设备进行初级供电,从正极经过一个输入端肖特基二极管引入至Pin BAT,输入范围为2.2-32V,该二极管可在因短路引起的暂态电压跌落的情况下将设备与电池迅速隔离开,由所用电池的最大电压决定,例如24V的电池选择40V的二肖特基极管。Pin VCC作为设备的第二级电源输入,连接在CHG和DSG的FETs共漏极,当电池处于电量较低的状态,若PACK上有充电器,设备检测到BAT的电压低于VCC时,将使用充电器的能量作为电源供应。最后,第三级电源供应来自Pin PBI,作为暂态失电的瞬间的能量后备,该引脚通过一个2.2μF的电容接入地,其瞬间的能量来源即该电容上储存的能量。

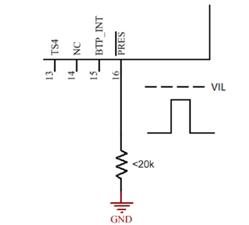

3.3系统检测

系统检测指BQ40z80通过Pin PRES*去检测PACK是否有充电器或负载的接入,该引脚通常接入地。设备内部通过一个典型值为10-20μA的电流源在该引脚每秒提供一个4μs的脉冲,为使该测试脉冲值低于VIL限制,应串联20kΩ或小于20kΩ的电阻,如图3-4所示。

图3-4 系统检测电路

同时,由于系统检测信号连接至PACK,为在外部静电放电时保护设备,BQ40z80的Pin PRES*内部已有集成ESD保护,仅需将一个1kΩ的电阻接入即可实现8 kV的ESD保护。

3.4 内部电压均衡

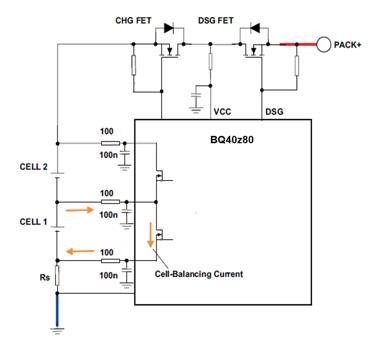

BQ40z80含有内部集成的电压均衡模块,可同时对每一节电芯实现最大10mA的均衡电流以达到电压均衡。

如图3-5所示,以两节电芯为例,当BQ40z80通过输入端的电压采样判断出某一节或多节电芯的电压异常时,将驱动内部旁路FETs,使其开通,在单节电芯的两端构成一个回路,所形成的旁路电流通过回路上的电阻将电芯两端异常的电压以热的形式消耗掉。因此,回路上的总电阻决定旁路电流的大小,即电压均衡的强度。

图3-5 内部集成电压均衡模块

电阻由两部分构成,第一是旁路FETs的导通电阻Rds(on)=200Ω,第二是电芯电压输入端的RC滤波电路。所以,每一节电芯的总旁路电阻为2×100+200 = 400Ω,若按一节电芯电压典型值为4V考虑,旁路电流约为10mA。需注意的是,电压均衡的实现过程并不是旁路FETs全导通直至均衡完成的过程,而是在每小时内以一定的占空比开启旁路FETs,对BQ40z80而言其典型值为75%,该值可通过软件进行修改。此时,对一节容量为2000mAh、SOC异常10%的电池,以占空比D去均衡则所需的时间t =2000mAh×10%/(10mA×D)。

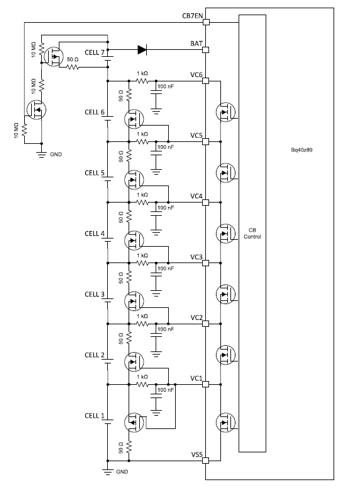

3.5 外部电压均衡模块

BQ40Z80含有内部集成的电压均衡模块,能同时对每一节电芯实现最大10mA的均衡电流以达到电压均衡。若需要更快速度的电压均衡能力,则需进行外部电压均衡模块的设计,如图3-6所示。

外部N-MOSFETs采用具备低栅源驱动阈值电压Vgs(th)的。考虑到FETs的导通稳定性,此处将输入RC滤波电路中原100Ω的电阻改变为1kΩ。工作原理如下:当BQ40z80控制内部旁路FETs导通,形成内部旁路回路,其上两个1kΩ的电阻和FETs的导通电阻Rds(on)=200Ω构成一个分压比为0.454的电阻分压器。考虑一节电芯的典型电压范围为3-4.2V,当进行单节电芯的电压均衡将会经过分压在电阻上产生一个1.362-1.907V的电压信号,该信号即外部FETs的栅源驱动电压,因此N-MOSFETs导通,外部的旁路回路打开,旁路电流大小将由外部回路上的电阻决定,用户可根据需求设置。

图3-6 外部电压均衡模块

应注意的是外部旁路MOSFET选择原则是在考虑电路分压比的情况下使其具备尽量低的Vgs(th),以实现成功可靠的驱动,例如DMN2004DWK、NTZD3154N和Si1024X等。更多细节可参考应用技用文档,Fast Cell Balancing Using

External MOSFET (SLUA420)。

3.6 温度

BQ40z80提供四个多达4个温度输入信号TS1、TS2、TS3和TS4,可同时用于电池、FETs等的温度检测,可通过软件配置其检测的对象类型和模式。 Pins TS1、TS2、TS3和TS4内部都集成了典型值18kΩ的上拉电阻,可支持25℃下10kΩ的NTC热敏电阻(暂不支持PTC),应注意用于电池的温度检测则常采用引线式热敏电阻,便于贴合电池表面,对电池温度达到更好的监控效果。

4 针对大电流场合的应用

在一些特殊的应用场合,如电动车、飞机等,通常要求的放电电流较高。据此,以下提供一些关于如何针对大电流的应用场合对BQ40z80进行电路设计的方案可供参考。

4.1 FETs及采样电阻并联方案

针对大电流放电设计的关键点在于如何拓展主电流回路承受电流的能力,即包括该回路上的充放电FETs和电流采样电阻。当要求FETs通过较大电流时,考虑到散热压力及MOS的额定电流,推荐使用并联MOS方案。在选型时,首先应考虑驱动能力的限制而选取具备尽量小的Qg的开关管,同时兼顾大电流导通情况下散热和损耗压力而选择具备尽量小的Rds(on)的开关管。但对于并联MOS易于产生的均流问题还需进行额外的考虑,如Layout时在尽量使其驱动信号位置平行。

针对电流采样电阻,BQ40z80本身是支持并联方案的。在选型时,应结合所需求的电流值和Pins SRP、SRN的输入电压范围的考虑去选取合适的电阻值。同时,出于散热考虑对额定功率和封装的选择建议留有一定裕量。例如实现对100A电流的采样,选取两个1mΩ、额定功率3W、2512封装的电阻。但出于对于电流采样精度的考虑,并联方案下对保障可靠的开尔文连接是至关重要的。

4.2 并联驱动能力解决方案

显然,并联MOS方案存在的最大问题就是IC驱动能力有限制,BQ40z80的Pins CHG、DSG的驱动最大输出负载能力约为10μA,可参考该值及MOS的输入电容、导通电阻等对其驱动能力进行衡量。针对该问题有如下两个解决方向:

第一,在BQ40z80的Pins CHG、DSG能力范围内去选择Qg值满足可成功驱动、Rds(on)满足和散热需求的MOSFET,但需注意的是,普遍而言,这两个值具备一个相反的关系,需要进行衡量。另外,此时MOS开通时间会相应变长。例如若选取CSD18510Q5B,Qg=118nC,Rds(on)=0.79mΩ(Vgs=10V),在以3个并联的方式使用时,导通时间约14ms。

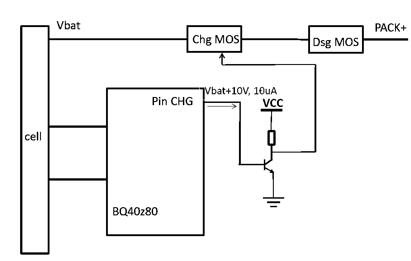

第二,当MOS的驱动需求超出BQ40z80的驱动能力或对开通时间有更高的要求的时候,可采用以下2种方式通过外加器件的设计增强电路驱动能力:

(1)在Pins CHG、DSG的输出增加一个额外的三极管去增强其驱动能力,如图4-1所示,但此时需增加一个额外的输出值高于Vbat大约10V左右的DC-DC去完成三极管的电源供应,上拉电阻阻值也应根据MOS驱动电流的需求设计。

图4-1 BQ40z80及三极管驱动电路

(2)增加高侧N通道FET驱动器BQ76200(BQ76200)去增强其驱动能力,如图4-2所示,该设计下将避免加额外的DCDC的需求,BQ40z80的Pins CHG和DSG的输出信号不再直接驱动MOS,而是作为BQ76200的使能输入,使用后者去驱动MOS,从而解决驱动能力不足的问题。

图4-2 BQ40z80及BQ76200驱动电路

选择该设计方案时应需注意,BQ40z80的Pins CHG和DSG的输出电平分别以Vbat和PACK+作为基准,而BQ76200的使能输入是以VSS作为基准,两者之间的电压等级并不匹配,所以需要进行电平转换。对于BQ9006驱动输出的高电平,需要使用一个电阻分压器R1、R2对BQ40z80的输出电压进行变换,使其符合BQ76200的使能输入范围。同时,对于BQ006 输出的低电平,需通过一个P-FET确保只有当Pin CHG的输出高于Vbat时,P-FET导通,BQ76200才会通过电阻分压器得到的使能输入,避免误导通现象。P-FET的选取原则是其Vgs(th)约为10V左右,与Pin CHG的驱动输出相对应。

其次,还需关注电阻分压器的阻值选取,考虑到Pin CHG的输出电流能力极限约为10μA,输出电压约为Vbat+10V,R1、R2的总阻值应限制电流在其能力范围内。同时,也应考虑BQ76200的使能输入Pin CHG_EN内部含有的一个典型值约为1MΩ的下拉电阻对分压值的影响。

在实现电平转换的基础上,需对BQ76200在并联方案下的电路进行进一步设计。首先,BQ76200除了支持充放电FETs串联连接,还支持充电和放电分为两个单独的回路,即充放电FETs并联的连接方式。当应用场合放电和充电的电流等级相差较大,可考虑分别设计充电和放电回路,这样的设计可以有效减少充电FETs的数量。确定何种连接方式后,应根据所使用FETs具体情况计算其Pin VDDCP上的电容值,更多细节可参考技术应用手册FET Configurations for the bq76200 High-Side N-Channel FET Driver(SLVA729A)。

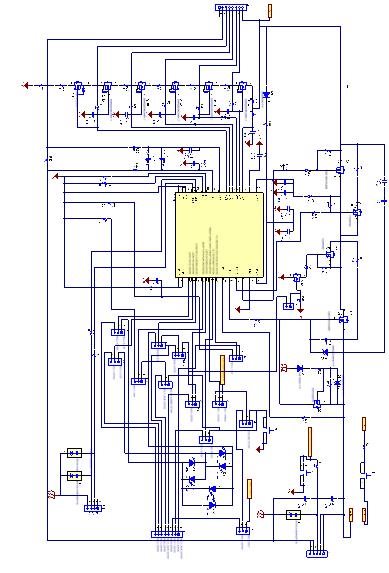

5 参考电路图

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。

相关推荐

电路设计[FPGA]设计经验

同步时序电路设计

揭秘 PCB 设计与制造过程

设计使用开源工具的芯片:Silicluster 的发展

频繁炸机,找原因?驱动电路原理分析

面向工业控制应用的同步整流高压buck调节器

桥接差距:为何设计者-制造商合作在 PCB 制造中至关重要

LED-74HC164驱动的LED显示电路设计(共阴)

Pmod兼容的可插拔外设模块

PCB\\protel\\Protel 99SE电路设计技术入门与应用

富士IGBT智能模块的应用电路设计

滤波器和衰减器的电路设计

数字AGC电路设计

从Layout设计看匹配艺术与布局优化

死铜是否要保留?(PCB孤岛)

ESD防护与电路设计

PCB走线应该走多长?

[转帖]基于PSD系列芯片的单片机电路设计

ModelGauge电量计

上海集成电路设计研究中心获ARM内核授权

电路设计常用软件介绍

6B595驱动的LED显示电路设计(共阳)

5.8GHz微波接收机电路设计

你画PCB为什么老返工?这些事情没做好!!!

加速电路设计的软件

高速数字电路PCB“接地”的要点

中国集成电路设计行业从业人员必备

低噪声放大器的选用与电路设计

利用模拟开发工具生态系统进行安全电路设计

非隔离式开关电源PCB布局设计技巧