- 工作中遇到一个关于电平选择的问题,居然给忘记RS232电平的定义了,当时无法反应上来,回来之后查找资料才了解两者之间的区别,视乎两年多的时间,之前非常熟悉的一些常识也开始淡忘,这个可不是一个好的现象,还是把关于三种常见的电平的区别copy到这里.做加深记忆的效果之用..

什么是TTL电平、CMOS电平、RS232电平?它们有什么区别呢?一般说来,CMOS电平比TTL电平有着更高的噪声容限。

(一)、TTL电平标准

输出 L: 2.4V。

输入 L: 2.0V

TTL器件输

- 关键字:

TTL RS232

- 熟悉一下数字电路一些问题,从细节入手,温故而知新。

1、什么是同步逻辑和异步逻辑,同步电路和异步电路的区别是什么?

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。

电路设计可分类为同步电路和异步电路设计。同步电路利用时钟脉冲使其子系统同步运作,而异步电路不使用时钟脉冲做同步,其子系统是使用特殊的“开始”和“完成”信号使之同步。由于异步电路具有下列优点--无时钟歪斜问题、低电源消耗、平均效能而非最差效能、模块

- 关键字:

数字电路 TTL

- MOS管一个ESD敏感器件,它本身的输入电阻很高,而栅-源极间电容又非常小,所以极易受外界电磁场或静电的感应而带电(少量电荷就可能在极间电容上形成相当高的电压(想想U=Q/C)将管子损坏),又因在静电较强的场合难于泄放电荷,容易引起静电击穿。静电击穿有两种方式:一是电压型,即栅极的薄氧化层发生击穿,形成针孔,使栅极和源极间短路,或者使栅极和漏极间短路;二是功率型,即金属化薄膜铝条被熔断,造成栅极开路或者是源极开路。JFET管和MOS管一样,有很高的输入电阻,只是MOS管的输入电阻更高。 静电放电形成

- 关键字:

MOS 击穿

- 本篇文章介绍了在逻辑IC中CMOS和TTL出现多余输入端的解决方法,并且对每种情况进行了较为详细的说明,希望大家能从本文得到有用的知识,解决输入端多余的问题。 CMOS门电路 CMOS门电路一般是由MOS管构成,由于MOS管的栅极和其它各极间有绝缘层相隔,在直流状态下,栅极无电流,所以静态时栅极不取电流,输入电平与外接电阻无关。由于MOS管在电路中是一压控元件,基于这一特点,输入端信号易受外界干扰,所以在使用CMOS门电路时输入端特别注意不能悬空。在使用时应采用以下方法: 与门和与非门电路 由

- 关键字:

CMOS TTL

- TTL电平信号对于计算机处理器控制的设备内部的数据传输是很理想的。COMS集成电路的许多基本逻辑单元都是用增强型PMOS晶体管和增强型NMOS管按照互补对称形式连接的,下面来说一下两者的区别。 什么是TTL电平 TTL电平信号被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑"1",0V等价于逻辑"0",这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。 TTL电平信号对于计算机处理器控制

- 关键字:

TTL CMOS

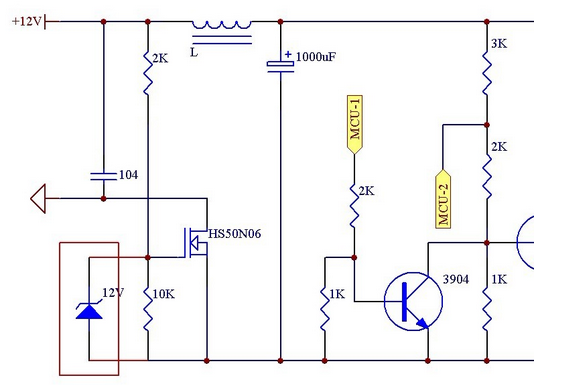

- 前段时间开发了一个产品,由单片机控制对负载供电,满负载时基准电流为800毫安,程序提供不同的供电模式,具体是由单片机输出一个PWM信号控制MOS管,从而按要求调整工作电流。我们知道MOS管导通时内阻非常小,我们所用的型号约为0.1欧姆的样子,这样正常工作时上面最大压降非常小,只有800毫安*0.1欧姆=0.08伏,上面的功率损耗为0.064瓦,对于电源控制来说是一种效果不错的器件。 虽然MOS管导通内阻非常小,但所流过的电流也有最大限制,如果电流过大,比如外接负载短路,同样会被烧毁。短路都是非正常工

- 关键字:

防短路 MOS

- 我们常接触到晶体三级管,对它的使用也比较熟悉,相对来说对晶体场效应管就陌生一点,但是,由于场效应管有其独特的优点,例输入阻抗高,噪声低,热稳定性好等,在我们的使用中也是屡见不鲜。我们知道场效应晶体管的种类很多,根据结构不同分为结型场效应管和绝缘栅型场效应管;绝缘栅型场效应管又称为金属氧化物导体场效应管,或简称MOS场效应管. 1、如何防止绝缘栅型场效应管击穿 由于绝缘栅场效应管的输入阻抗非常高,这本来是它的优点,但在使用上却带来新的问题.由于输入阻抗高,当带电荷物体一旦靠近栅极时,在栅极感应出来的

- 关键字:

场效应晶体管 MOS

- 一.TTL TTL集成电路的主要型式为晶体管-晶体管逻辑门(transistor-transistor logic gate),TTL大部分都采用5V电源。 1.输出高电平Uoh和输出低电平Uol Uoh≥2.4V,Uol≤0.4V 2.输入高电平和输入低电平 Uih≥2.0V,Uil≤0.8V 二.CMOS CMOS电路是电压控制器件,输入电阻极大,对于干扰信号十分敏感,因此不用的输入端不应开路,接到地或者电源上。CMOS电路的优点是噪声容限较宽,静态功耗很小。

- 关键字:

TTL CMOS

- 随着数字电路向高集成度、高性能、高速度、低工作电压、低功耗等方向发展,数字电路中的△I噪声正逐步成为数字系统的主要噪声源之一,因此研究△I噪声的产生过程与基本特点,对认识△I噪声特性进而抑制△I噪声具有实际意义。 反相器是数字设计的核心。本文从反相器入手,分析了TTL和CMOS中△I噪声的产生过程与基本特点。 1 △I噪声的产生 1.1 TTL中△I噪声的产生 TTL反相器的基本电路如图1所示。在稳定状态下,输出Vo分别为高电平VOH和低电平VOL时,电源提供的电流IH和I

- 关键字:

TTL CMOS

- [问]:

1、电阻电容的封装形式如何选择,有没有什么原则?比如,同样是 104 的电容有 0603、0805 的封装,同样是 10uF 电容有 3216、0805、3528 等封装形式,选择哪种封装形式比较合适呢?

2、有时候两个芯片的引脚(如芯片A 的引脚 1,芯片B 的引脚 2)可以直接相连,有时候引脚之间(如A-1 和 B-2)之间却要加上一片电阻,如 22欧,请问这是为什么?这个电阻有什么作用?电阻阻值如何选择?

3、藕合电容如何布置?有什么原则?是不是每个电源引脚布置一片

- 关键字:

封装 TTL

- 本文主要介绍了什么是负电压及如何产生,希望对您的学习有所帮助。

1、电荷泵提供负压

TTL电平/232电平转换芯片(如,MAX232,MAX3391等)是最典型的电荷泵器件可以输出较低功率的负压。但有些LCD要求-24V的负偏压,则需要另外想办法。可用一片max232为LCD模块提供负偏压。TTL-in接高电平,RS232-out串一个10K的电位器接到LCM的VEE。这样不但可以显示, 而且对比度也可调。 MAX232是+5V供电的双路RS-232驱动器,芯片的内部还包含了+5V及&pl

- 关键字:

负电压 TTL

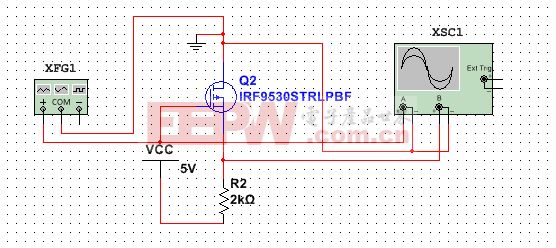

- 当我们还是学生的时候,不论从做题还是原理分析上,通常会重点学习NPN和PNP三极管的特性:静态工作特性计算、动态信号分析等等。对于MOS管,老师一般都会草草带过,没有那么深入的分析和了解,一般都会说MOS管和三极管的不同就是一个是电压控制,一个是电流控制,一个Ri大,一个Ri小等等。除了这些明显的特性,下文就从工作实战的角度进行MOS场效应管的分析。 首先我们来看下经常使用的增强型mos场效应管:N沟道和P沟道mos场效应管。 在消费类电子设计中由于对功耗要求比较严格,通常使用N沟道和P沟道MOS

- 关键字:

MOS 场效应管

- 本文介绍了上下拉电阻的作用、使用方法等问题。

重要信号线的上下拉问题

一般说来,不光是重要的信号线,只要信号在一段时间内可能出于无驱动状态,就需要处理。

比如说,一个CMOS门的输入端阻抗很高,没有处理,在悬空状况下很容易捡拾到干扰,如果能量足够甚至会导致击穿或者闩锁,导致器件失效。祈祷输入的保护二极管安全工作吧。如果电平一直处于中间态,那输出就可能是不确定的情况,也可能是上下MOS都导通,对器件寿命造成影响。

总线上当所有的器件都处于高阻态时也容易有干扰出现。因为这时读写控制

- 关键字:

CMOS TTL

- 所有MOS集成电路(包括P沟道MOS,N沟道MOS,互补MOS—CMOS集成电路)都有一层绝缘栅,以防止电压击穿。一般器件的绝缘栅氧化层的厚度大约是25nm50nm80nm三种。在集成电路高阻抗栅前面还有电阻——二极管网络进行保护,虽然如此,器件内的保护网络还不足以免除对器件的静电损害(ESD),实验指出,在高电压放电时器件会失效,器件也可能为多次较低电压放电的累积而失效。按损伤的严重程度静电损害有多种形式,最严重的也是最容易发生的是输入端或输出端的完全破坏以至于与

- 关键字:

MOS 集成电路

- 现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲

- 关键字:

TTL,CMOS

ttl-mos介绍

您好,目前还没有人创建词条ttl-mos!

欢迎您创建该词条,阐述对ttl-mos的理解,并与今后在此搜索ttl-mos的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473