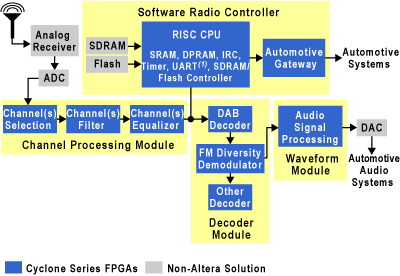

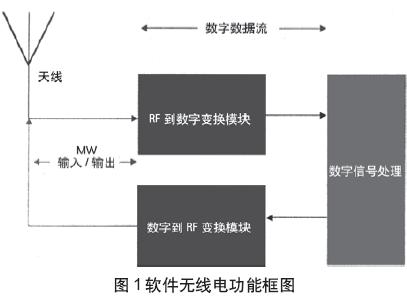

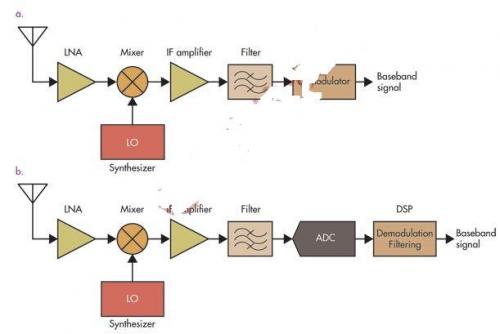

软件无线电(SDR)是指发射方的调制和接收方的解调都使用软件来完成的一种无线通信方式。每一个SDR的接收器都会在通过天线或一个中间界面以后加上一个模拟到数字(A/D)的信号转换器。

混音以及基带的处理都是以数字方式完成并通过软件来进行控制。这样一种操作模式的主要优点在于其高度的灵活性,因为软件完全可以在为任何一种接收器所设置的通用硬件平台上运行。设计人员可以通过这个通用的硬件平台提取所有接收器所共有的一组功能,或者在加入新的接收器时,设计人员可以根据需要选择对硬件进行重新设置。

图1显示了

关键字:

汽车电子 软件无线电 SDR 转换器

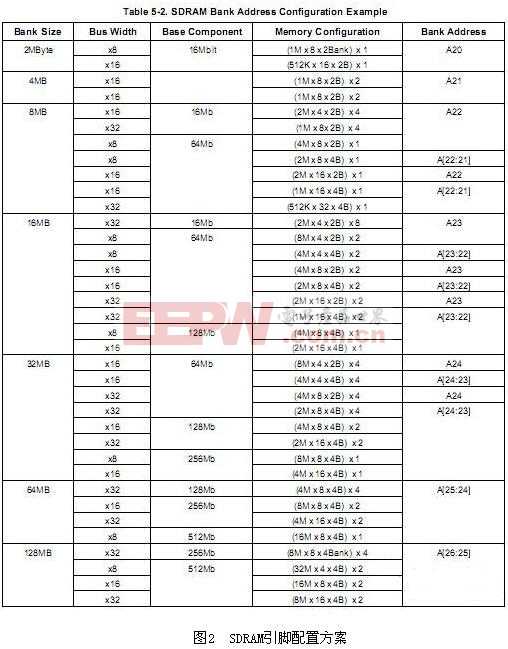

RAM(随机存取存储器 是一种在电子系统中应用广泛的器件,通常用于数据和程序的缓存。随着半导体工业的发展,RAM获得了飞速的发展,从RAM、DRAM(Dynamic RAM,即动态RAM)发展到SDRAM(Synchronous Dynamic RAM,即同步动态RAM),RAM的容量越来越大、速度越来越高,可以说存储器的容量和速度已经成为半导体工业水平的标志。

1 任务背景

SDRAM具有大容量和高速的优点,目前其存取速度可以达到100~133MHz,单片容量可以达到64Mbit或更高

关键字:

VHDL SDRAM 存储器 微处理器

在高速数字视频系统应用中,使用大容量存储器实现数据缓存是一个必不可少的环节。SDRAM就是经常用到的一种存储器。

但是,在主芯片与SDRAM之间产生的时序抖动问题阻碍了产品的大规模生产。在数字电视接收机的生产实际应用中,不同厂家的PCB板布线、PCB材料和时钟频率的不同,及SDRAM型号和器件一致性不同等原因,都会带来解码主芯片与SDRAM间访问时序的抖动问题。

本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使

关键字:

SDRAM 数字电视

随着笔记本电脑、手机等移动终端以及家用数码产品的大规模增长,器的移动性和能耗问题已广泛受到业界关注。日前,(全球半导体组织)委员会会议在上海举行,推动存储工业新标准制定。

在过去五年内,JEDEC曾与中国半导体行业组织合作,促进中国及世界的半导体行业标准。例如中国电子标准协会(CESA),中国半导体行业协会(CSIA)与中国电子标准研究所(CESI)等。

我国企业已占JEDEC会员数的20%,而且数目还在增长。JEDEC本次会议主要研究了DDR3 SDRAM(第三代双倍速率同步动态随机存储

关键字:

SDRAM DRAM

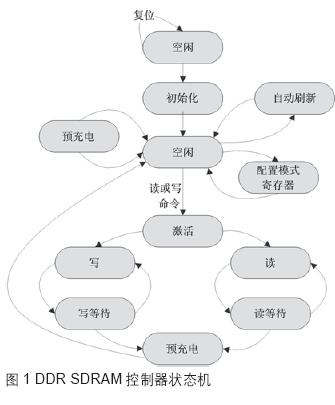

实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera公司Cyclone系列的FPGA完成了对DDR SDRAM的控制,以状态机来描述对DDR SDRAM的各种时序操作,设计了DDR SDRAM的数据与命令接口。用控制核来简化对DDR SDRAM的操作,并采用自顶至下模块化的设计方法,将控制核嵌入到整个数据采集系统的控制模块中,完成了数据的高速采集、存储及上传。使用开发软件Quartus II中内嵌的逻辑分析仪SignalTap II对控制器的工作流程进行了验证和调试。最终采集到的

关键字:

FPGA DDR SDRAM 数据采集

合成仪器(SI)利用部件开放结构环境中所用的核心硬件和软件构建单元组合,合成传统仪器中的激励和/或测量功能。合成仪器概念在70年代末和80年代初,主要是集中在军事项目研究中。此时,其技术不能为商业提供可用性。所能实现的主要是集中在RF/微波应用中的低频模拟、数字和基带中。

现代合成仪器发现它们的根是在过去10年通信革命和呈现出的软件无线电(SDR)概念中。根据SDR的定义,SDR是由DSP、发送器、接收器把数字数据变为无线通信用的调制无线电波和把调制无线电波变换为数字数据。DSP提供无线电功能,

关键字:

合成仪器 SI SDR

拉斯维加斯——德尔福公司与世界空间卫星广播公司(简称世广,WORLDSPACE® Satellite Radio)于今日宣布:双方已达成有关协议,德尔福公司将在世广开发的基础上,为欧洲配件市场设计首部世广卫星广播移动接收机。此外,双方公司宣布世广已选定德尔福为其欧洲整车厂接收机及接收系统应用项目的主要设计商,该项目也将在世广原有的设计基础上进行。德尔福于2008年国际消费类电子产品展览会上宣布了这一消息。 德尔福设计的该款接收机专为欧洲售后市场设计,用来接收覆盖整个欧洲大陆的世

关键字:

德尔福 世广 卫星数字广播 SDR

随着设计与制造技术的发展,集成电路设计从晶体管的集成发展到逻辑门的集成, 现在又发展到IP的集成,即SoC设计技术。SoC可以有效地降低电子信息系统产品的开发成本,缩短开发周期,提高产品的竞争力,是工业界将采用的最主要的产品开发方式。目前国内也加大了在SoC 设计以及IP 集成领域的研究。本文介绍的便是国家基金项目支持的龙芯SoC—ICT- E32 设计所集成的片上SDRAM 控制器模块设计与实现。

1 ICT-E32 体系结构

ICT-E32 是一款32位高性能SoC ,它集成龙芯1号

关键字:

SoC SDRAM 控制器 MCU和嵌入式微处理器

DDR3 SDRAM内存的总线速率达到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作电压,采用90nm制程达到2Gbits的高密度。这个架构毫无疑问更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling) 如果FPGA&nbs

关键字:

FPGA DDR3 SDRAM 接口 模拟IC 电源

恩智浦半导体 (NXP Semiconductors)推出一项重大技术创新——强大的完全可编程的矢量处理器,用于解决移动通信中的集成性、灵活性及标准问题。恩智浦的嵌入式矢量处理器(Embedded Vector Processor,EVP)使移动设备能够支持多模式与多标准的平台,同时还能够兼容各种层出不穷的电信标准。这对正处于从 3G 向 4G 过渡时期的手机制造商来说尤为关键。

恩智浦半导体首席技术官 Rene Penning de Vries 表示:“我们正从 3G 向 4G 演进,各种无线

关键字:

通讯 无线 网络 恩智浦 半导体 SDR 消费电子

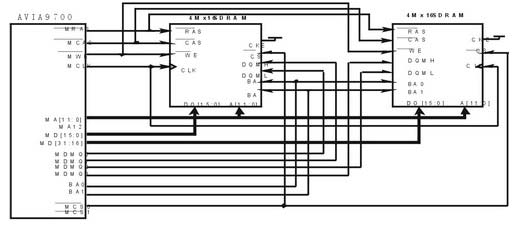

在高速数字视频系统应用中,使用大容量存储器实现数据缓存是一个必不可少的环节。SDRAM就是经常用到的一种存储器。

但是,在主芯片与SDRAM之间产生的时序抖动问题阻碍了产品的大规模生产。在数字电视接收机的生产实际应用中,不同厂家的PCB板布线、PCB材料和时钟频率的不同,及SDRAM型号和器件一致性不同等原因,都会带来解码主芯片与SDRAM间访问时序的抖动问题。

本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使

关键字:

嵌入式系统 单片机 SDRAM 时序控制 MCU和嵌入式微处理器

引言 同步动态随机存储器(SDRAM),在同一个CPU时钟周期内即可完成数据的访问和刷新,其数据传输速度远远大于传统的数据存储器(DRAM),被广泛的应用于高速数据传输系统中。基于FPGA的SDRAM控制器,以其可靠性高、可移植性强、易于集成的特点,已逐渐取代了以往的专用控制器芯片而成为主流解决方案。然而,SDRAM复杂的控制逻辑和要求严格的时序,成为开发过程中困扰设计人员主要因素,进而降低了开发速度,而且大多数的基于FPGA的SDR

关键字:

工业控制 嵌入式系统 单片机 FPGA SDRAM 嵌入式 工业控制

1 引言随着雷达技术发展,大带宽高分辨力、多种信号处理方式的采用,使得实时信号处理对数据的处理速度大大提高。同时在雷达信号处理中运算量大,数据吞吐量急剧上升,对数据处理的要求不断提高。随着大规模集成电路技术的发展,作为数字信号处理的核心数字信号处理器(DSP)得到了快速的发展和应用。ADSP-TS201DSP是美国模拟器件(ADD公司继TSl01之后推出的一款高性能处理器。此系列DSP性价比很高,兼有FPGA和ASIC信号处理性能和指令集处理器的高度可编程性,适用于大存储量、高性能、高速度的信号处理和图像

关键字:

模拟技术 电源技术 SDRAM DSP-TS201 总线接口 模拟IC 电源

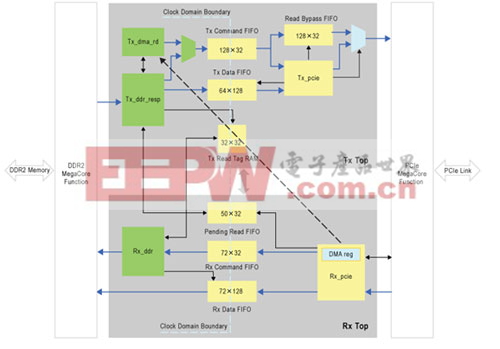

Altera PCI Express到DDR2 SDRAM 参考设计,OverviewAltera offers a PCI Express to DDR2 SDRAM reference design that demONSTrates the operation of Alteras PCI Express (PCIe) MegaCorereg; product. This reference design provides an interface betw

关键字:

参考 设计 SDRAM DDR2 PCI Express Altera

Altera宣布,在FPGA业界实现了对高性能DDR3存储器接口的全面支持。在最近通过的JESD79-3 JEDEC DDR3 SDRAM标准下,Altera Stratix® III系列FPGA可以帮助设计人员充分发挥DDR3存储器的高性能和低功耗优势,这类存储器在通信、计算机和视频处理等多种应用中越来越关键。

这些应用处理大量的数据,需要对高性能存储器进行快速高效的访问。符合JESD79-3 JEDEC DDR3 SDRAM标准可满足DDR3存储器的1.5V低功耗电压供电要求,在下一

关键字:

Altera SDRAM 存储器

ref-sdr-sdram介绍

您好,目前还没有人创建词条ref-sdr-sdram!

欢迎您创建该词条,阐述对ref-sdr-sdram的理解,并与今后在此搜索ref-sdr-sdram的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473