- 摘要:分析了MV-D1024E系列高帧频CMOS相机的工作时序和参数,阐述了CAMERA-LINK接口协议,并对高速数据流的存储与处理机制进行分析,利用FPGA实现了相机的数据接口和控制,并设计灵活的USB接口,利用PC机作为参数输入

- 关键字:

FPGA 1024 MV-D 相机的

- 电脑绣花机是随着计算机技术、电子技术、机械加工技术的应用发展而不断发展起来的光、机、电一体化设备。嵌入式系统的发展及研究风头正劲,其在数字机床、智能控制等方面的应用正逐渐改变着传统的工业生产和服务方

- 关键字:

FPGA ARM 电脑绣花机 控制系统

- 1、前言 随着计算机技术的高速发展,各工业发达国家投入巨资,对现代制造技术进行研究开发,提出了全新的制造模式,其核心思想之一是柔性化制造,制造系统能够随着加工条件的变化动态调整。目前,各类MCU 快速

- 关键字:

CPLD DSP 可重构 仿真

- 随着工艺节点和裸片尺寸不断缩小,采用倒装芯片封装IC器件的消费电子产品的数量日益增加。但是,倒装芯片封...

- 关键字:

SoC 设计 封装协同 芯片 FPGA

- 据EDA Consortium(EDAC)的统计,第一季度全球EDA收入下滑至11.9亿美元,同比减少10.7%。

同步大幅下滑的主要原因是Cadence调整了其会计模式。

与去年第四季度的13.2亿美元相比,第一季度EDA收入降9.9%。EDAC主席、Mentor Graphics公司主席兼CEO Walden Rhines表示,EDA每年第一季度的收入都会环比下滑。

Rhines指出,10.7%的同比下滑幅度较去年第四季度的18%有所减小,这可能说明EDA先于芯片产业开始回暖。

- 关键字:

Mentor EDA 芯片

- 介绍了一种利用ALTERA公司的复杂可编程逻辑器件(CPLD)快速卷积法实现数字滤波器的设计。

- 关键字:

CPLD FIR 数字滤波器

- 介绍了一款PC104总线多功能扩展卡设计。采用了复杂可编程逻辑器件(CPLD)技术,集成了多路模拟量输入/输出、带光电隔离的开关量输入/输出及一个正交解码电路,接口协议与台湾研华PC工控机ISA总线板卡兼容,满足了嵌入式控制系统高集成度的设计要求,在实际应用中获得了良好的效果。

- 关键字:

CPLD 104 PC 总线

- 高性能系统设计师在满足关键时序余量的同时要力争获得更高性能,而存储器>存储器接口设计则是一项艰巨挑战。双倍数据速率SDRAM和4倍数据速率SDRAM都采用源同步接口来把数据和时钟(或选通脉冲)由发射器

- 关键字:

FPGA 助力 存储器 接口设计

- 摘要:现代通信系统中,数字化已成为发展的必然趋势,数字信号处理则是数字系统中的重要环节。在数字信号处理方面提出一种级联信号处理器的FPGA实现方案,用以取代昂贵的专用数字处理芯片。首先对级联信号处理器做了

- 关键字:

FPGA 级联 信号处理器

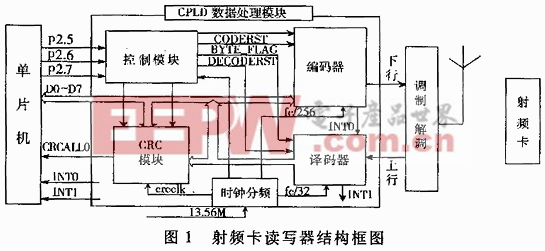

- 提出了一种射频卡读写器数字处理模块的设计方案,特点是利用单片CPLD器件实现了读写器编码、译码和差错处理功能,系统体积小,性能稳定。该方案采用了原理图和VHDL相结合的灵活设计,给出了一种快速CRC-CCITT并行实现的方法。

- 关键字:

应用 读写器 射频卡 CPLD 射频

- 先进的视频编码(AVC)正在慢慢地超越数字视频的主要标准。也称之为H.264和MPEG-4part10,其AVC编码在1Mbit/s~2...

- 关键字:

视频编码器 AVC编码 FPGA

- 摘 要:选用Altera公司的可编程逻辑器件EPF10K10LC84-4作为硬件电路。依据EDA技术的设计思想,运用VHDL硬件描述语言和Max+PlusⅡ软件,针对数字频率计的工作原理,对其各个部分进行编程。该设计结构清晰,避免了用原

- 关键字:

EDA 数字频率计

- 数字信号处理模块是接收机系统的核心部分,系统要求数字信号处理模块能实时处理ADC变换后的数字信号,并用软件的方法来实现大量的无线电功能,这些功能包括:多通道校准、编解码、调制解调、滤波、同步、盲均衡、

- 关键字:

FPGA 多通道 校准 算法

fpga-cpld-eda介绍

您好,目前还没有人创建词条fpga-cpld-eda!

欢迎您创建该词条,阐述对fpga-cpld-eda的理解,并与今后在此搜索fpga-cpld-eda的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473