摘要:介绍了一种利用USB2.0的高速传输特性,基于USB和DSP的数据采集系统。详细论述了系统的总体结构、部分硬...

关键字:

USB DSP FPGA

“我感到目前半导体企业正面临一个问题,就是他们不了解应用,更不要说多个相互衔接的应用了。这使他们与系统客户之间出现了一个‘断裂带’,发展受到了限制。”今年4月,有30多年半导体行业经验的恩智浦执行副总裁TheoClaasen先生对《中国电子报》记者说。其实,很多半导体巨头都已经看到了这一点,并采取了向系统方案纵向延伸的战略,使自己更加接近客户。在可编程逻辑器件(FPGA)领域,赛灵思(Xilinx)公司也正在努力从一家器件厂商向一家要深入了解应用的方案厂

关键字:

Xilinx FPGA IC设计 ISE

FPGA(现场可编程逻辑器件)产品的应用领域已经从原来的通信扩展到消费电子、汽车电子、工业控制、测试测量等广泛的领域。而应用的变化也使FPGA产品近几年的演进趋势越来越明显:一方面,FPGA供应商致力于采用当前最先进的工艺来提升产品的性能,降低产品的成本;另一方面,越来越多的通用IP(知识产权)或客户定制IP被引入FPGA中,以满足客户产品快速上市的要求。此外,FPGA企业都在大力降低产品的功耗,满足业界越来越苛刻的低功耗需求。

第一时间采用新工艺提升性能降低成本

半导体产品的集成度和成本

关键字:

FPGA ASIC SRAM 低功耗

随着产品对成本、性能、尺寸、安全性和功耗等要求不断提高,FPGA(现场可编程门阵列)的应用也逐渐增多。近年来,整个可编程逻辑器件产业的增长速度几乎是整个半导体产业增速的两倍。同时,随着中国在全球市场地位日益突出,各大FPGA厂商也加紧在亚太区尤其是中国市场精耕细作。

提升服务品质 深耕中国市场

赛灵思公司亚太区市场及应用总监 张宇清

在新任首席执行 官 MosheGavrielov的带领下,赛灵思在中国将获得战略性成长,增长更迅速。同时,依托中国经济的迅速增长,赛灵思还将继续通过优秀

关键字:

FPGA PLD

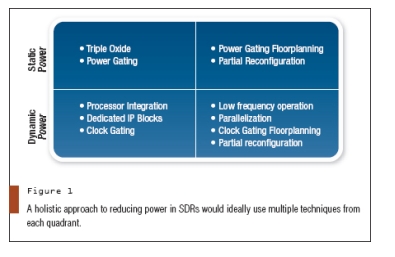

由于像美国联合战术无线电系统(JTRS)这样的计划,软件定义的无线电(SDR)早已被证实。然而,有许多问题严重地制约着SDR的广泛部署,其中相当重要的问题就是功率。

功率是在设计每一个SDR子系统时的主要考虑因素,特别是因为它们要消耗比硬件无线电更多的功率。例如,为了获得预期的无线电通信距离(依赖于链路的状况,典型值为5-10千米数量级),射频(RF)前端必须具备足够的发射功率。同样,对于靠电池工作的无线电设备,RF前端、调制解调器和加密处理子系统的功耗都直接影响无线电设备的寿命。此外,对由调制

关键字:

FPGA 无线电 SDR 功耗

视频监控系统是火车站、机场、银行、娱乐场所、购物中心甚至家庭保安的重要组件。随着安全风险增加,对视觉监视和记录事件的需求以多种使用模式激增。因此,新架构必须为横跨一整套日渐繁杂的视频监控系统要求的成本效益方案提供可扩展性。

上市时间的压力、新CODEC标准、日益广泛的要求(包括先进的目标探测、运动探测、目标跟踪和目标跟踪特性),这些不过是新型视频监控架构所面临挑战中的几项。伴随挑战而来的是对可扩展为不同性能范围的实现的需求。

对于从低端到高端以及从单机到PC扩展卡的任何视频

关键字:

视频监控 DVR FPGA Xilinx

NI 日前隆重发布了可应用于控制、测试及嵌入式系统开发的图形化系统设计平台的最新版本——LabVIEW 8.6。得益于LabVIEW软件平台天生并行的图形化编程方式,LabVIEW 8.6版本提供了全新工具帮助工程师和科学家们从多核处理器、现场可编程门阵列 (FPGAs) 及无线通信等商业技术中获益。

目前,为了能够使用这些最新技术,工程师们往往不得不使用非专为并行编程设计的软件工具。而最新版的LabVIEW则为他们提供了独立的平台,通过采用多核处理器技术提高

关键字:

NI LabVIEW 8.6 嵌入式 FPGA

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:

超声波 液体密度 FPGA 声速法

引言

对于码分多址的扩频通信方式而言,只有当接收端本地伪码与发端伪码处于相同相位状态时,有用的信息才能被解出。因此,扩频序列相位的捕获与跟踪是扩频通信系统的关键,而伪码序列相位的捕获尤为重要。滑动相关法是常用的方法之一。扩频通信系统要求实时性,以及较高的数据处理速度,这正是FPGA的优势。所以在扩频通信系统中,大量应用FPGA芯片作为前级处理芯片。

实现原理

原理分析

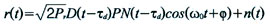

接收机端接收到的扩频信号可以表示为:

其中,P_{r}为接收信号功率,τ_{d}为传输时延,

关键字:

FPGA 扩频通信 多址 滑动相关法

前言

调相脉冲信号可以获得较大的压缩比,它作为一种常用的脉冲压缩信号,在现代雷达及通信系统中获得了广泛应用。随着近年来软件无线电技术和电子技术的发展,DDS(直接数字频率合成)用于实现信号产生的应用越来越广。DDS技术从相位的概念出发进行频率合成,它采用数字采样存储技术,可以产生点频、线性调频、ASK、PSK及FSK等各种形式的信号,其幅度和相位一致性好,具有电路控制简单、相位精确、频率分辨率高、频率切换速度快、输出信号相位噪声低、易于实现全数字化设计等突出优点。

目前,DDS的ASIC芯片如

关键字:

FPGA 信号源 ASIC QPSK DDS

引言

DDR3 SDRAM存储器体系结构提高了带宽,总线速率达到了600 Mbps至1.6 Gbps (300至800 MHz),它采用1.5V工作,降低了功耗,90-nm工艺密度提高到2 Gbits。这一体系结构的确速率更快,容量更大,单位比特的功耗更低,但是怎样才能实现DDR3 SDRAM DIMM和FPGA的接口呢?调平技术是关键。如果FPGA I/O结构中没有直接内置调平功能,和DDR3 SDRAM DIMM的接口会非常复杂,成本也高,需要采用大量的外部元件。那么,什么是调平技术,这一技

关键字:

FPGA 存储器 DDR3 SDRAM

Altera公司宣布,松下公司在P2 HD专业广播高清晰摄像机中选用了Cyclone® III FPGA。P2 HD AJ-HPX2700和P2 HD手持式AG-HPX170是松下公司为满足全球范围内对高清晰(HD)广播需求而开发的两款无磁带摄像机。

随着全球市场向HD的迈进,广播行业需要高清晰图像质量。在松下公司P2 HD专业广播高清晰摄像机中,Cyclone III FPGA提供HD视频处理功能,实现与P2存储卡的接口,并控制LCD显示屏。在所有低成本FPGA系列中,Cyclone

关键字:

Altera FPGA 高清 HD

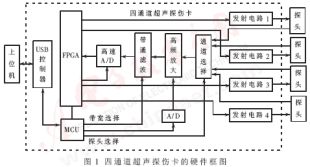

1 四通道超声探伤卡的总体结构

四通道超声探伤卡的总体结构框图如图1所示。从框图中可以看出,其主要由超声发射电路、通道选择、放大滤波、数据采集压缩、卡内微处理器、USB接口等部分组成。

四通道采用分时工作方式。四个通道分时进行超声发射,回波信号经过通道选择开关后进行信号放大与带通滤波,然后在FPGA的控制下进行A/D转换,采集的数据在FPGA内实时压缩后存入FPGA内部的双端口RAM中,然后由卡上的微处理器读取数据,再次进行数字滤波后通过USB接口向上位PC机传送。

2 超声波发射电路

关键字:

微处理器 探伤卡 FPGA 超声波

引言

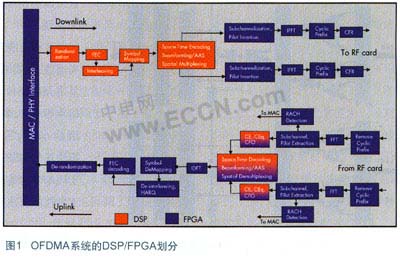

无线运营商通过提供增强数据服务来提高单位用户平均收益(ARPU),这同时推动了对宽带的需求,导致对数据速率的要求越来越高。而且,为用户提供各种应用体验的要求也促使底层网络体系结构进行变革。窄带2G GSM、IS-95系统等以语音为中心的技术已经发展到了基于WCDMA的HSDPA和HSUPA系统,峰值数据速率达到了10Mbps。今后的3GPP长期发展规范采用了多输入多输出(MIMO)等复杂的信号处理技术,以及正交频分复用接入(OFDMA)和多载波码分复用接入(MC-CDMA)等新的射频技术,这些

关键字:

MIMO WiMAX LTE 3G FPGA

fpga-1c6介绍

您好,目前还没有人创建词条fpga-1c6!

欢迎您创建该词条,阐述对fpga-1c6的理解,并与今后在此搜索fpga-1c6的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473