- 概述:

手动除颤通过给予心脏受控电击,迫使所有心肌瞬间收缩,从而有望使心脏恢复正常心律。历来只有经过专门培训的医疗专业人员才能够使用手动除颤器掌握心律。然而,自动体外除颤器 (AED) 使用嵌入式计算机芯片对心律进行即时而准确的分析,从而使非医疗专业人员在无意外电击风险的情况下也能提供同样重要的服务。

AED 器件轻盈小巧,可监视人的心律 (通过放在人身上的特殊垫子)并能够识别心脏 纤维性颤动 (VF),也称为“心脏骤停”,或 SCA。如果出现 SCA, AED 将

- 关键字:

医疗电子 自动体外除颤器 AED DSP

- 根据SRM工作原理,设计了基于DSP56F805的三相(6/4)SRM双闭环驱动系统。分析了一种三相SRM起动方法,对速度和电流环分别采用了积分分离PI控制算法和增量式PID控制算法。

- 关键字:

驱动 系统 设计 电机 磁阻 DSP 开关 基于

- 针对传统数字视频广播系统码流分析仪价格昂贵、使用不方便的问题,本文提出一种性价比较好的补充设计方案,它以通用的FPGA和RTOS为基础、基于嵌入式硬件平台来实现码流分析功能。文中还阐述了码流采集、码流分析和信息显示等多项关键技术。

码流分析仪可用作数字电视设备的调试工具,如检测MPEG编码器、复用器、调制解调器等设备的输入输出码流是否符合MPEG-2/数字电视广播(DVB)标准等。作为标准检验设备,码流分析仪是整个数字电视系统的不可缺少的重要设备。实际使用中的数字电视集成系统是一项庞大、复

- 关键字:

嵌入式 码流分析 FPGA RTOS

- 随着计算机技术的飞速发展,嵌入式图像系统广泛应用于办公设备、制造和流程设计、医疗、监控、卫生设备、交通运输、通信、金融银行系统和各种信息家电中。所谓嵌入式图像系统,指以图像应用为中心,以计算机技术为基础,软件、硬件可裁减,对功能、可靠性、成本、体积、功耗等严格要求的专用计算机系统。嵌入式图像系统对图像显示技术提出了各种严格要求,必须选择合适的显示器,设计出合理的显示控制方法。

系统硬件设计

本系统要构建一个嵌入式、高速、低功耗、低成本的图像显示硬件平台,要求能真彩显示静态或动态彩色图像。为

- 关键字:

DSP TFT-LCD 数字图像 显示技术 嵌入式 CPLD

- 0 引言

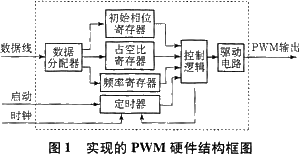

在许多嵌入式系统的实际应用中,需要扩展FPGA(现场可编程门阵列)模块,将CPU实现有困难或实现效率低的部分用FPGA实现,如数字信号处理、硬件数字滤波器、各种算法等,或者利用FPGA来扩展I/O接口,如实现多路PWM(脉宽调制)输出、实现PCI接口扩展等。通过合理的系统软硬件功能划分,结合优秀高效的FPGA设计,整个嵌入式系统的效率和功能可以得到最大限度的提高。

在电机控制等许多应用场合,需要产生多路频率和脉冲宽度可调的PWM波形。本文用Altera公司FPGA产品开发工具Quar

- 关键字:

FPGA 逻辑仿真 PWM

- 美国国家仪器有限公司(简称NI)推出4种用于PXI平台的新型R系列 I/O模块,这些模块都配备了高性能的Xilinx Virtex®-5现场可编程门阵列(FPGA)芯片。NI PXI-7841R, PXI-7842R, PXI-7851R 和PXI-7852R模块具有8个模拟输入、8个模拟输出和96个数字I/O通道,而且模拟输入的速率比以前版本的R系列设备快3.5倍以上。这些新型模块为工程师和科学家们提供了即时可用的硬件;不仅如此,这

- 关键字:

NI I/O模块 FPGA LabVIEW

- Altera公司近日发布了业界首款40nmFPGA(现场可编程门阵列)和HardCopyASIC(专用集成电路)。两者都提供收发器,在密度、性能和低功耗上遥遥领先。

StratixIV系列有680K逻辑单元,比Altera的StratixIII系列高两倍,是目前市场上密度最大的FPGA。器件满足了众多市场对各种高端应用的需求,例如无线和有线通信、广播和ASIC原型开发等。

- 关键字:

Altera 40nm FPGA

- 采用DSP(数字信号处理器)作为控制器,而采用USB(通用串行总线)和上位机相连接将是数据采集处理系统的一种可能的发展趋势。

- 关键字:

处理 理系 数据采集 技术 DSP USB 基于

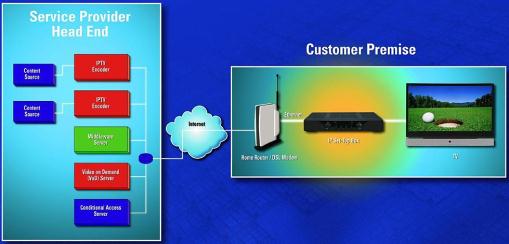

- 随着IPTV市场准备起飞,竞争生态系统数量的增加意味着STB开发商必须保持他们的实现方案选项具备开放性。

未来几年,由电信业务提供商推动的IPTV市场(利用互联网协议传输数字电视)有望形成规模。然而,目前该市场陷入了各种硬件和软件解决方案的竞争之中,不同种类的压缩技术非常复杂,并与家庭网络应用存在潜在的融合。这些因素使工程师在设计IP机顶盒的时候面临决策困难,所以原始设备制造商(OEM)需要选择处理技术,以使他们保持实现方案选项的开放性。

作为传输方案的焦点,STB必须能够适应它要部署的特

- 关键字:

IPTV STB DSP 机顶盒 视频编码 VOD

- 引言

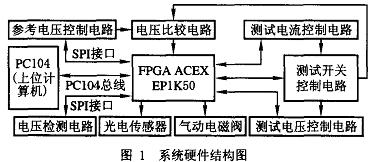

PCB 光板测试机基本的测试原理是欧姆定律,其测试方法是将待测试点间加一定的测试电压,用译码电路选中PCB 板上待测试的两点,获得两点间电阻值对应的电压信号,通过电压比较电路,测试出两点间的电阻或通断情况。 重复以上步骤多次,即可实现对整个电路板的测试。

由于被测试的点数比较多, 一般测试机都在2048点以上,测试控制电路比较复杂,测试点的查找方法以及切换方法直接影响测试机的测试速度,本文研究了基于FPGA的硬件控制系统设计。

硬件控制系统

测试过程是在上位计算机的控制下

- 关键字:

FPGA PCB 硬件电路 测试机

- 在嵌入式系统设计中常使用通用异步接收和发送器UART(Universal Asynchronous Receiver/Transmitter)实现系统控制信息或低速数据信息的传输,而UART所采用的奇偶校验方式不具备前向纠错能力,检错能力也有限,所以在设计UART时要尽可能提高其抗干扰能力,以加强系统的可靠性。

1 基于最佳接收的UART

目前UART中的接收器多采用如图1所示的设计。

同步模块

- 关键字:

UART 最佳接收 FPGA 同步模块 逻辑优化

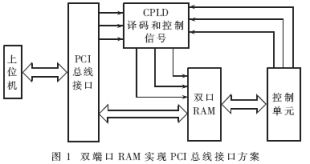

- 采用双端口RAM实现DSP与PCI总线芯片之间的数据交换接口电路。

提出了一种使用CPLD解决双端口RAM地址译码和PCI接口芯片局部总线仲裁的的硬件设计方案,并给出了PCI总线接口芯片寄存器配置实例,介绍了软件包WinDriver开发设备驱动程序的具体过程。

随着计算机技术的不断发展,为满足外设间以及外设与主机间的高速数据传输,Intel公司于1991年提出了PCI总线概念。PCI总线是一种能为主CPU及外设提供高性能数据通讯的总线,其局部总线在33MHz总线时钟、32位数据通路时,数据

- 关键字:

RAM DSP PCI总线 CPLD 数据通讯

- 你是否有过这样的经历:见到一个人后,整个世界一下子明亮起来。所谓的“华堂升辉”、人们所说的“光彩照人”,连又聋又瞎的海伦•凯勒都说“点亮了我心中的明灯”。

如果你还没有这样的经历,建议你去接触一下FPGA界的人士吧!在半导体业的星光大道上,FPGA行业绝对是个群星灿烂的领域。激发你获得灵感。

笔者多年前去美国参加一个会议,整日浸泡在英语的海洋中,非常boring。因此当采访了A公司和Q公司的市场人员,深受震撼。他们都是高大健美,高高的鼻梁,深邃的眼睛,年龄三、四十,你随便提

- 关键字:

FPGA 半导体

- 介绍了一种基于DSP与USB的高速数据采集与处理系统,包括整个系统的硬件设计与软件设计。DSP控制整个系统完成CCD信号采集并进行小波变换去噪处理,FPGA协同DSP实现整个系统的地址译码和逻辑控制。主机应用程序通过USB完成与DSP的数据通信,实现整个采集的控制和数据显示。这种高速的数据采集与处理系统,可广泛地应用于各种智能仪表、自动化控制设备中,有着非常好的市场应用前景。

- 关键字:

处理 理系 设计 数据采集 高速 DSP USB 基于

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473