回声消除(AEC)可实现汽车内舒适的全双工免提通话,本文介绍的Clarity CVC-HFK可提供集成的单扩音器解决方案(OMS)噪声抑制算法,它支持自适应噪声消除功能,可降低麦克风(传入)信号中的环境噪声,并提取所需的语音,还可向远端用户传输清晰的话音(传出)。

关键字:

信号处理 音频 系统 车载 开发平台 DSP 免提 采用

本系统用于油田测井过程中,对电缆所受的张力、油井的深度及电缆下井速度等参数的测量。重点阐述了系统结构及工作原理。

关键字:

测量 系统 速度 深度 DSP 张力 基于

引 言

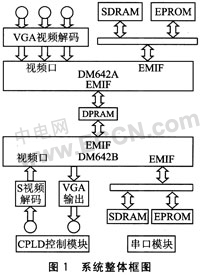

视频合成技术是图像处理方面的一个重要应用,它将一个图像的多个状态或者多幅不同图像进行合成,来实现虚拟面板、图像叠加、模拟场景、图像优化等效果。多路视频合成显示技术是将通过多个途径(如摄像机、PC机、网络等),采集而来的多路视频信号进行处理,并按照实际所需进行显示。

选择适当的核心处理芯片,对数据量大、实时性高的视频信号处理来说,是首要考虑的问题。美国TI公司推出的针对视频和图像解决方案的TMS320DM642型高性能数字媒体处理器,是TI公司C6000系列中一款基于DaVinci技

关键字:

DSP DM642 视频合成技术 TI 数字媒体处理器

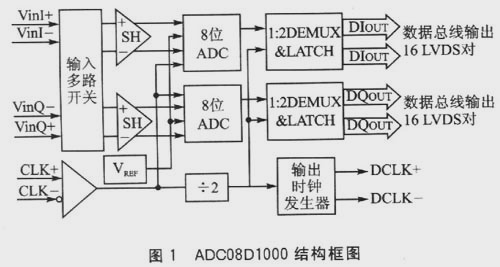

1 ADC08D1000的结构

ADC08D1000是NS(National Semiconductor,国家半导体)公司于2005年推出的双通道低功耗的高速8位A/D转换器,其最高单通道采样频率达l.3 GHz,全功率带宽(FPBW)为1.7 GHz,在500 MHz标准信号输入的情况下可以获得7.4位的有效采样位数。整个A/D转换器用单电源1.9V供电,内带高质量参考源和高性能采样保持电路,每个通道均为差分输入,采样范围可选为650 mV或870 mV(峰一峰值)。在高速数/模转换系统中,有

关键字:

硬件电路 NS A/D转换器 FPGA LVDS

基于DSP芯片TMS320F2812的电机控制器设计,描述了其引导加载ROM、AD转换单元、传感器接口、cpld等电机控制外设电路的技术关键。还简单介绍了其在调速系统中的应用。

关键字:

设计 应用 控制器 DSP TMS320F2812 基于

FPGA工艺尺寸的进步和更加灵活的设计配置、以及基于FPGA的系统取得的进步已经使FPGA制造商充满信心地进入了以前由微处理器和ASIC供应商垄断的市场。最近,Xilinx的VirtexTM和Altera的Stratix产品系列分别推出了新器件,进一步缩小了性能差距,再次提高了性能标准。尽管这些器件的通用和可配置性吸引了系统设计师,但是控制这些器件内部工作方式的设计规则及其外部接口协议的复杂性导致需要广泛的培训、基准设计评估、设计仿真和验证。因此,FPGA供应商提供了详尽的硬件和固件支持,旨在帮助系统设计

关键字:

DC/DC ,解决方案,FPGA

安富利公司 (NYSE: AVT) 旗下安富利电子元件部宣布推出Xilinx® Virtex®-5 FXT FPGA 评估工具套件。该套件以Xilinx最新的Virtex-5 FXT 现场门阵列(FPGA)为基础,还包括了一块评估板、ISE® Design Suite 10.1 WebPACK™ 设计工具、评估版Embedded Development Kit (EDK)软件、电源并能获得参考设计和设计指南等资料。此套件成本低廉,是意图研究Virtex-5 FXT平

关键字:

安富利公司 安富利电子元件部 Xilinx FPGA 评估工具套件

对基于数字信号处理器(DSP)的系统而言,优化功耗是一项重要但往往难以实现的设计目标。现在,基于DSP的设备常常把以往各自独立的多个应用结合起来,每一个应用都可能有多个工作模式。要得到这样一个设备的功率分布是非常困难的一件事,更遑论整个复杂的系统。设计人员需要获知尽可能多的最佳信息,以及能够帮助他们优化特定应用之功耗的技术和工具。

关键字:

功耗 优化 设计 DSP 处理 嵌入式 如何

0 引言

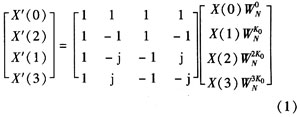

有限长序列的DFT(离散傅里叶变换)特点是能够将频域的数据离散化成有限长的序列。但由于DYT本身运算量相当大,限制了它的实际应用。FFT(快速傅里叶变换)算法是作为DFT的快速算法提出,它将长序列的DFT分解为短序列的DFT,大大减少了运算量,使得DFT算法在频谱分析、滤波器设计等领域得到了广泛的应用。

FPGA(现场可编程门阵列)是一种具有大规模可编程门阵列的器件,不仅具有专用集成电路(ASIC)快速的特点,更具有很好的系统实现的灵活性。FPGA可通过开发工具实现在线编程。与C

关键字:

FPGA FFT 集成电路 DFT

0 引言

数字图象处理技术在电子通信与信息处理领域得到了广泛的应用,设计一种功能灵活、使用方便、便于嵌入到系统中的视频信号采集电路具有重要的实用意义。

在研究基于DSP的视频监控系统时,考虑到高速实时处理及实用化两方面的具体要求,需要开发一种具有高速、高集成度等特点的视频图象信号采集系统,为此系统采用专用视频解码芯片和复杂可编程逻辑器件(CPLD)构成前端图象采集部分。设计上采用专用视频解码芯片,以CPLD器件作为控制单元和外围接口,以FIFO为缓存结构,能够有效地实现视频信号的采集与读取

关键字:

DSP 数据采集 视频采集 CPLD 数字图象处理

提出了一种直接利用DSP的MCBSP接口和DMA通道实现UART的方法,给出了使用C语言和CSL的编程方法。与传统实现方法相比,具有实现成本低,硬件电路简单,移植性强等特点,稍加修改可应用于C5000和C6000各系列芯片中。

关键字:

通信 设计 UART DSP TMS320C55x 基于

基于DSP实现MP3解码系统的设计,采用高性能的立体声音频Codec芯片TLV320AIC23作为音频信号数模转换,DSP的两个McBSP与其连接,分别作为配置接口和音频数字接口,配置接口设置为SPI模式。USB与DSP接口实现MP3数据流与PC机之间的上传与下载,存取MP3文件方便,存储MP3文件的媒介选取大容量的存储设备CF卡,系统选用可编程逻辑器件CPLD控制USB及CF卡的读写和片选。实验证明该系统可以高质量完成MP3解码、播放。

关键字:

系统 设计 解码 MP3 DSP 基于

本文详细描述了在TI (Texas Instruments) C55x系列DSP平台上集成实时实现0.3kbps至16kbps多种速率语音编解码算法的方法,及在现有C语言源代码基础上优化汇编指令的技巧。

关键字:

设计 实现 DSP 算法 语音 解码 制式

Altera公司今天宣布,Stratix® III FPGA在其LVDS I/O上支持串行千兆位介质无关接口(SGMII)。Stratix III LVDS I/O的接口速率达到1.25 Gbps,满足SGMII严格的抖动性能要求,支持不含收发器的三速以太网(10/100/1000 Mbps)接口。Stratix III FPGA是业界首款在LVDS引脚上支持千兆以太网SGMII的可编程逻辑器件,降低了每个器件的成本和功耗,提供更多的接口。

Stratix III FPGA的SGMII

关键字:

Altera Stratix III FPGA SGMII 以太网

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473