- 0引言数据采集和控制系统是对生产过程或科学实验中各种物理量进行实时采集、测试和反馈控制的闭...

- 关键字:

FPGA 数据采集

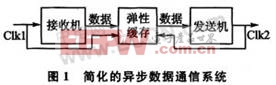

- 引 言一个简化的异步数据通信系统如图1所示。接收机端从接收到的来自串行链路的比特流中提取时钟信号Clk1,作为其工作时钟源;而发送机端采用本地晶振和锁相环产生的时钟Clk2,作为其工作时钟源。接收机在时钟Clk1的

- 关键字:

设计 弹性 FPGA 系统 FC-AL

- 继去年 9 月发布基于 NanoBoard 3000 的快速原型设计全新方案后,Altium日前又宣布推出采用 Altera Cyclone III® FPGA 的最新 NanoBoard 3000,从而进一步扩展了这一理念。

新的开发板为电子设计人员继续提供相同的软硬件以及 NanoBoard 3000 可以直接使用的免专利费 IP,所不同的是,在其内核中提供了具有 Altera 高性价比 Cyclone III® FPGA 电源。

电子设计人员采用 NanoBoard

- 关键字:

Altium FPGA NanoBoard

- Tensilica宣布即将推出基于HiFi 架构的新一代产品HiFi EP音频DSP,可同时支持家庭娱乐产品中的多声道编解码以及持续扩展的音频前/后处理等应用,如:蓝光播放器、数字电视(DTV)以及智能手机。HiFi EP增强了高效率、高质量的语音前、后处理功能,与同类产品相比,HiFiEP最多可以减少40%的功耗及50%的芯片面积。Tensilica将于2010年2月15-18日西班牙巴塞罗那举行的全球移动大会展出其HiFi EP音频DSP(数字信号处理)引擎,展位号:7C35。

HiFi 2

- 关键字:

Tensilica DSP HiFi

- 首先与实测系统功耗进行对比,验证了Xilinx公司ISE软件包中FPGA功耗估算工具XPower的准确性。然后对FPGA设计中影响系统功耗的几个相互关联的参数进行取样,通过软件估算不同样点下的系统功耗,找到功耗最低的取样点,得到最佳设计参数,从而达到优化系统设计的目的。实验中通过这种方法,在一个FPGA读写SRAM的系统中,在单位时间读写操作数固定的条件下,选取了读写频率与读写时间占空比这两个参数来优化系统功耗。最终测试数据证明了该方法的正确性。

- 关键字:

FPGA 低功耗 电子 系统优化

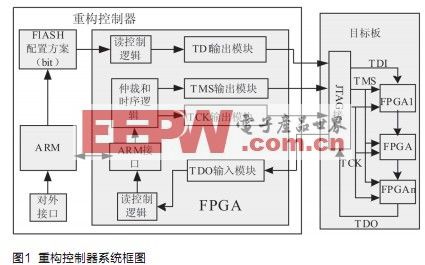

- 为充分利用硬件资源,满足不同的应用需求,本文提出了一种基于JTAG边界扫描模式配置的重构控制器,详细介绍控制器的硬件实现以及配置流程,该控制器通过模拟JTAG接口时序及TAP状态机的功能,实现在系统配置目标可编程器件。

- 关键字:

FPGA TAP状态机 JTAG边界扫描 重构 201001

- 随着2010年的来临,当今的全球电子公司纷纷做出明智而审慎的研发投资决定,以便借助创新的新产品,快速抓住新的市场机遇。FPGA越来越多地成为这些公司成功的关键。除了少数可超大批量生产的商品外,应用ASIC的高成本和高风险无法让绝大多数的商品赢利;现在面临着加速替代ASIC所带来的机遇,这主要体现在以下不同方面:芯片体系结构,也就是能够推出某种架构和相关的I/O,而且,密度和性能还能够达到一定水平,从而可以替代ASIC的功能。 软件在加速替代ASIC过程中也扮演了重要角色。高效的软件和设计工具大大提高了

- 关键字:

赛灵思 FPGA ASIC 摩尔定律

- 据业者透露,台积电公司将于今年中期开始为Altera公司生产28nm制程FPGA芯片产品。这种FPGA芯片将集成有28Gbps收发器,产品面向云计算,在线存储以及移动视频等应用,Altera公司两年前曾推出该系列产品的 40nm制程版本。台积电还宣布其28nm制程将为全代制程(full node:即制程升级时需要对芯片电路进行重新设计),而且年内其28nm制程还将具备可按客户的需求制作出HKMG(High-K绝缘层+金属栅极)或SiON(SiON绝缘层+硅栅极)这两种不同栅极结构的能力.

台积电

- 关键字:

台积电 28nm FPGA Altera

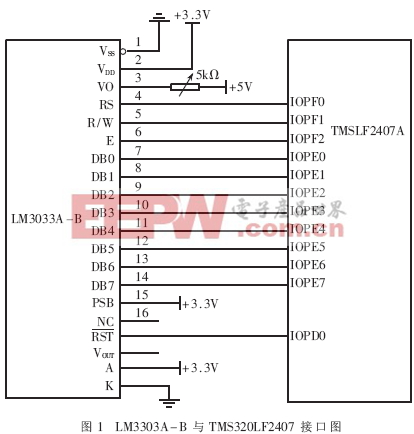

- 基于DSP和ST7920的液晶显示模块的实现, DSP是一种适合于数字信号处理的实时高速的高性能微处理器,已广泛应用于自动控制、图像处理、通信技术、网络设备、仪器、仪表和家电领域。液晶显示屏以其显示直观、便于操作的特点被用作各种便携式系统的显示终端。

- 关键字:

模块 实现 液晶显示 ST7920 DSP 基于

- 理解FPGA 中的压稳态 本白皮书介绍FPGA 中的压稳态,为什么会出现这一现象,它是怎样导致设计失败的。介绍怎样计算压稳态MTBF,重点是对结果造成影响的各种器件和设计参数。

引言

当信号在不相关或者异步时钟域

- 关键字:

FPGA 压稳态

- 人们对宽带服务的带宽要求越来越高,促使芯片供应商使用更多的高速串行收发器。因此,下一代应用采用了多种数据速率,从几Mbps 到数百Gbps,在一种设备中集成了多种协议和服务。以太网等迅速发展的标准以及对提高

- 关键字:

FPGA ASIC 40 nm

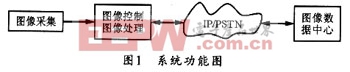

- 介绍了基于SOPC技术的嵌入式数字图像处理系统的设计方法,该系统以Alteral公司的Nios嵌入式软件处理器为核心来分别对图像的采集、存储,图像处理,显示等功能模块进型结构设计,最后把处理数据通过网络发送到接收端,从而完成了利用嵌入式系统和Internet技术的信息沟通。

- 关键字:

处理 理系 设计 图像 数字 FPGA MB86S02 基于

- 本工程设计完全符合IP核设计的规范流程,而且完成了Verilog HDL建模、功能仿真、综合、时序仿真等IP核设计的整个过程,电路功能正确。实际上,本系统在布局布线后,其系统的最高时钟频率可达80MHz。虽然使用浮点数会导致舍入误差,但这种误差很小,可以忽略。实践证明,本工程利用流水线结构,方便地实现了高速、连续、大数据量浮点数的加法运算,而且设计结构合理,性能优异,可以应用在高速信号处理系统中。

- 关键字:

FPGA 流水线 浮点 加法器

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473