- 给出异步FIFO电路在高速数据采集系统中的应用,由FPGA生成独立时钟域的FIFO缓存器,采用FIFO的可编程设置参数启动数据传输,根据读写时钟频率异同的传输要求和FIFO的特性,采用一套控制电路,解决了可变速率数据缓存和固定时钟传输的问题。

- 关键字:

FIFO FPGA 时钟 201004

- 爱特梅尔公司(Atmel Corporation)宣布推出全新浮点单元(Floating Point Unit)技术,用于爱特梅尔32位AVR UC3产品系列。此新技术可使设计师在汽车和工业控制等应用中,采用一个爱特梅尔微控制器(MCU)可以取代传统微控制器和数字信号处理器(DSP) 两芯片方案。

爱特梅尔的32位AVR UC3微控制器特色之一,是其架构具有非常高的数字信号处理性能。UC3 MCU提供通常只在高端DSP才有的定点和整数算法,因而性能超出大部份的微控制器。通过增加一个准确的浮点单元

- 关键字:

Atmel AVR DSP 浮点单元

- G.723.1算法在DSP上的优化,1 引言 G.723.1是删组织于1996年推出的一种低码率的语音编码算法标准,也是目前该组织颁布的语音压缩标准中码率最低的一种标准。G.723.1主要用于对语音及其它多媒体声音信号的压缩,目前在一些数字音视频传输、高

- 关键字:

优化 DSP 算法 G.723.1

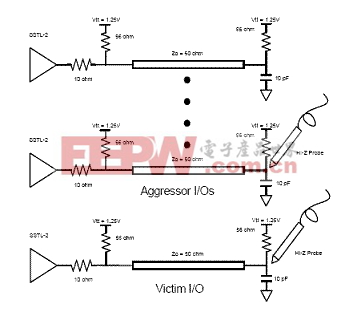

- FPGA上同步开关噪声的分析, 概述 随着半导体技术的快速发展,近年来FPGA 的器件容量和输入输出的管脚数量都极大的增加了,例如StratixIV 器件,最大的一款EP4SE680 拥有68.11 万个逻辑单元和1104个输入输出管脚。大量的输出管脚在同一时刻

- 关键字:

分析 噪声 开关 同步 FPGA

- 摘 要:本文在分析目前使用的GPS定位系统的基础上,探讨了一种替代系统,系统通过接收不同城市广播电台的发出的报时信号,算出这些地方距离定位设备所在地的距离,进而确定本地的确切地理位置,设计了系统的FPGA实现

- 关键字:

FPGA GPS 定位 系统

- 全球领先的硅产品知识产权 (SIP) 平台解决方案和数字信号处理器 (DSP) 内核授权厂商CEVA公司宣布,授权业界领先的4G 芯片组制造商 Sequans Communications 公司使用CEVA-X1641 DSP 内核,助力 Sequans 下一代 LTE 和 WiMAX 基带处理器中。CEVA-X1641 内核将为Sequans下一代基带芯片提供更大的灵活性,同时仍保持业界领先的低额定功率。

Sequans Communications工程技术副总裁Bertrand Debray

- 关键字:

CEVA DSP 4G

- 当今的嵌入式应用已经无处不在,全球每年生产数十亿颗微处理器,其中大部分被广泛应用于各类嵌入式系统,从消费电子、通信终端及系统设备、工业控制、汽车电子系统到航空航天,无处不能看到嵌入式应用的身影。在硬件平台方面微控制器以及数字信号处理器(DSP)产品无论从品牌、成本、功能特性方面选择数以千计,您完全可以针对您的目标应用对成本、处理能力、功耗要求、集成度、开发周期、技术难度等具体要求,精心选择出最具综合优势的硬件核心平台。而在嵌入式操作系统方面,您同样不再会有桌面应用中几乎无可选择的尴尬,无论是开放源代码

- 关键字:

ADI DSP Blackfin

- 全球领先的硅片知识产权(SIP)平台解决方案和数字信号处理器(DSP)内核授权厂商CEVA公司宣布,三星电子公司(Samsung Electronics Co., Ltd)已在其第一代商用LTE(Long Term Evolution)调制解调器中采用CEVA DSP内核技术,这款调制解调器在20MHz带宽下支持高达100Mbps的下载速率和高达50Mbps的上载速率。三星电子最近推出采用这种调制解调器的LTE 宽带无线适配器(dongle)产品,目前在瑞典斯德哥尔摩和挪威奥斯陆已经投入商用。

- 关键字:

CEVA DSP LTE

- 基于嵌入式DSP应用的低功耗优化策略, 无线系统及有线系统设计师均必须重视电源效率问题,尽管双方的出发点不尽相同:对于移动设备而言,更长的电池使用寿命、更长的通话时间或更长的工作时间都是明显的优势,降低电源要求意味着使用体积更小的电池或选

- 关键字:

优化 策略 功耗 应用 嵌入式 DSP 基于

- 基于DSP与FPGA的跟踪伺服运动控制,摘 要: 在分析光电跟踪伺服系统特点的基础上,以TI公司DSP芯片TMS320F2812作为主控制芯片,采用FPGA进行逻辑时序控制,设计了基于DSP和FPGA的多轴伺服运动控制器。给出了该控制器的功能和硬件结构以及软件流程设计

- 关键字:

运动 控制 伺服 跟踪 DSP FPGA 基于

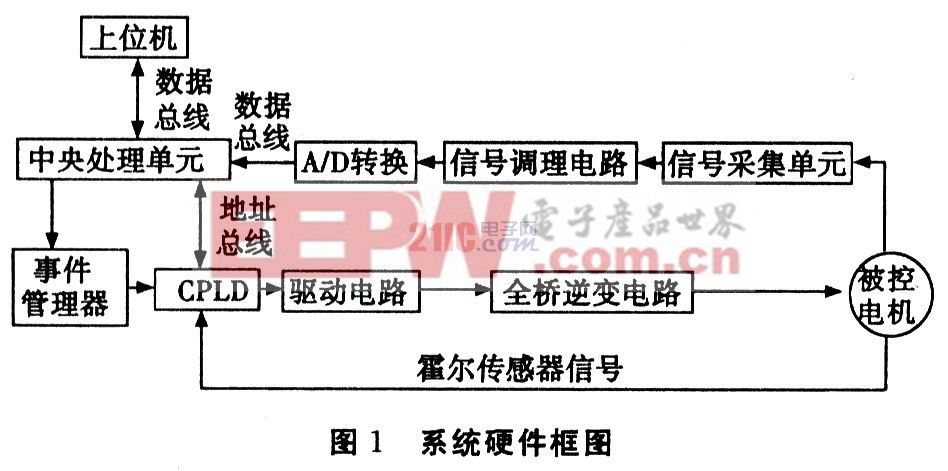

- 基于DSP的无刷直流电动机的模糊控制系统研究,摘要:介绍一种数字信号处理器(DSP)控制的无刷直流电机控制系统。利用TMS320IF2407的运动控制接口形成单片DSP控制的电机系统。采用霍尔元件检测转子磁极位置,形成电子换相逻辑。由pi进行速度和电流控制,用模糊逻辑

- 关键字:

控制系统 研究 模糊 直流电动机 DSP 基于

- 摘要:介绍了基于高性能DSP芯片ADSP21161和S3C2410 ARM芯片实现的电能质量分析仪的设计方法。以DSP芯片为核心实现数据采集及处理,以S3C2410芯片为核心实现数据管理、人机界面及系统控制,同时采用WinCE嵌入式操作系

- 关键字:

DSP ARM 便携式 电能质量

- 摘要:设计了以TMS320F2812DSP芯片为核心的无刷直流电机伺服控制系统。采用电流环,速度环,位置环三闭环控制,对位置环采用积分分离的PID算法,以减小电机在运行过程中积分校正对系统动态性能的影响。为加快系统响应

- 关键字:

伺服系统 设计 电机 直流 DSP BLDC

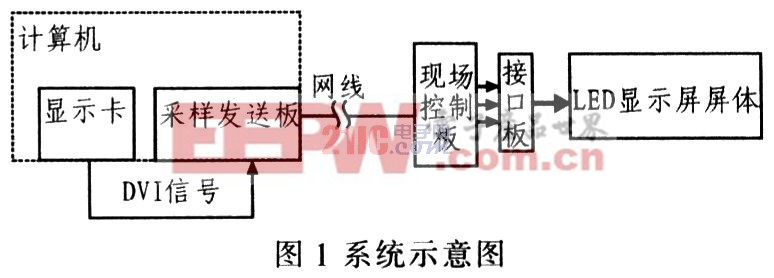

- 摘要:介绍一种以FPGA为核心,基于网口传输的全彩高灰度同步LED显示屏控制系统的设计方法。该设计改变传统设计中低效高成本的信号采集和传送方式,改用实时采集DVI接口显示信号、通过网口传输数据,采用高集成度FPGA

- 关键字:

FPGA 实现 控制系统 同步 传输 LED

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473