- 摘要:针对电路设计中经常碰到数据的噪声干扰现象,提出了一种Kalman滤波的FPGA实现方法。该方法采用了TI公司的高精度模数转换器ADSl25l以及Altera公司的EPlCl2,首先用卡尔曼滤波算法设计了一个滤波器,然后将该滤波

- 关键字:

Kalman FPGA 滤波器

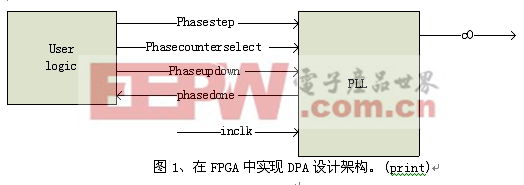

- 在低成本FPGA中实现动态相位调整,在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自带有DPA电路,但低端的FPGA,如CYCLONE(r)系列中是没有的。本文主

- 关键字:

相位 调整 动态 实现 FPGA 成本

- 莱迪思半导体公司今日宣布Nu Horizons Electronics Corp. 即日起将在全球范围内代理莱迪思的全部产品。Nu Horizons目前在整个亚太地区代理莱迪思产品。

Nu Horizons全球代理部总裁Kent Smith 表示:“Nu Horizons Electronics 非常高兴能与莱迪思一起拓展全球业务。莱迪思是全球领先的FPGA、PLD、可编程时钟和电源管理器件、软件设计工具和IP核供应商之一,并且我们的全球销售和工程师团队对于可编程逻辑技术非常了解。莱

- 关键字:

莱迪思 FPGA PLD 可编程时钟 电源管理器件

- 摘要:本文提出了一种基于FPGA的图像裁剪电路的设计方法,利用像素的抽取改变图像的分辨率,从而达到图像裁剪的效果。与传统的方法相比,这种方法简单易行,开发成本低,图像的清晰度能满足一定的要求。此方法数据处

- 关键字:

FPGA 图像 裁剪 电路

- 摘要:为了解决PCI9052和双口RAM之间读写时序不匹配的问题,本设计采用可编程器件来实现它们之间的接口电路。此电路可以使系统更加紧凑。核心逻辑部分采用有限状态机实现,使控制逻辑直观简单,提高了设计效率。

通

- 关键字:

FPGA PCI9 RAM PCI

- 引言随着信息化和数字化的发展,现在社会中人们的生活变得更加丰富多彩,生活更加便利。但是有一种...

- 关键字:

FPGA 智能导盲犬

- Analog Devices, Inc.,全球领先的高性能信号处理解决方案供应商,最新推出32位浮点数字信号处理器SHARC产品组合的最新成员——SHARC 2148x及SHARC 2147x系列。 高性能SHARC 2148x及低功耗SHARC 2147x系列处理器凭借集成高达5Mb 的存储器,为各种应用提高了单芯片、浮点信号处理精度,并为便携式设备实现了高端系统功能。 通过SHARC 2148x及SHARC 2147x处理器,设计师可以利用端到端 SHARC 系列的代码兼容

- 关键字:

ADI DSP SHARC

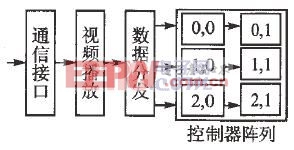

- 目前,显示屏按数据的传输方式主要有两类:一类是采用与计算机显示同一内容的实时视频屏;另一类为通过USB、以太网等通信手段把显示内容发给显示屏的独立视频源显示屏,若采用无线通信方式,还可以随时更新显示内容,灵

- 关键字:

视频 LED 系统 独立 全彩 ARM FPGA 甚于

- IPTV视频广播中采用FPGA作为编码和解码平台的好处是明显的。然而,为FPGA供电可能是一个挑战,而采用根据电源要求设计的专用电源管理器件,如MIC68200,将极大地缩短新系统的上市时间。

- 关键字:

供电 问题 FPGA 系统 IPTV 基于 通信协议

- 全球领先的硅产品知识产权 (SIP) 平台解决方案和数字信号处理器(DSP)内核授权厂商CEVA公司宣布提供CEVA-SATA3.0设备控制器IP。基于与固态硬盘 (SSD) 客户广泛的合作经验,CEVA公司已经提升其SATA设备控制器IP性能,提供 6Gbps 线路速率 (line rate) 以实现更快的数据传输,使得吞吐量较上代产品提高一倍。该IP已经授权予一家领先的闪存半导体制造商,用于其未来的固态硬盘设计中。

CEVA-SATA3.0 IP 采用最新的原生指令排序 (Native Co

- 关键字:

CEVA 固态硬盘 DSP

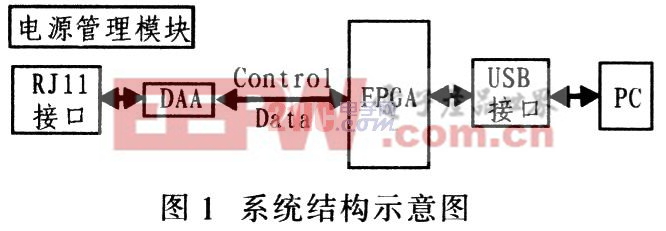

- FPGA的嵌入式系统USB接口设计,摘要:设计基于FPGA的IP-BX电话应用系统,用于传统的电话网络(PSTN)与PC机之间的接口连接。USB2.0接口器件EZ-USB FX2 CY7C68013A-56工作在slave FIFO模式,为基于FPGA的嵌入式系统与PC机之间提供数据和命令通道,从

- 关键字:

接口 设计 USB 系统 嵌入式 FPGA

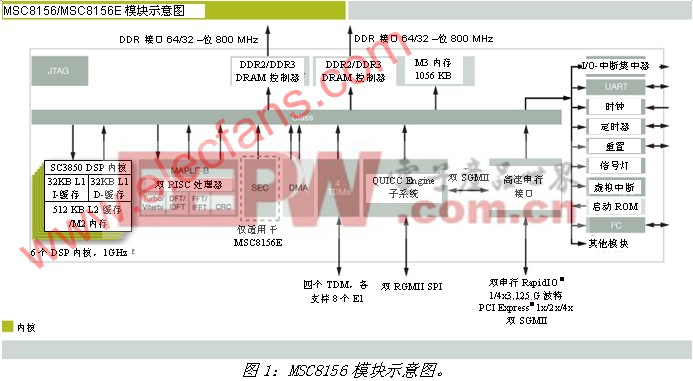

- DSP实现3G LTE应用技术简介,3G LTE是第三代伙伴计划(3GPP)的一个高级标准,为广域网提供下一代宽带无线技术。 与以前各阶段的3GPP相比,3G LTE的目标是更高的吞吐量、更低的时延以及高效的IP回程,提供一种新的可以大规模部署的移动网络技术,预

- 关键字:

应用技术 简介 LTE 3G 实现 DSP

- 对许多包含并行性或可流水化的算法而言,由于裕量连接带宽可实现用户自定义的数据通路,这样,逻辑可在一个时钟周期内访问存储器或访问另一个逻辑块的结果,从而使FPGA的持续性能可接近峰值性能。由于固定架构具备预先确定的用以实现不同功能的逻辑块集合,所以可以为FPGA配置支持某种给定算法的最优逻辑函数比例来实现器件资源的最佳利用。

- 关键字:

进展 处理 FPGA 交换

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473