- 不管是放到测试设置中,还是作为被测设备的一部分,时钟恢复都在进行准确的测试测量时发挥着重要作用。由于大多数千兆位通信系统都是同步系统,因此系统内部的数据都使用公共时钟定时。不管是沿着几英寸的电路板传送

- 关键字:

PLL 时钟恢复 设计方案

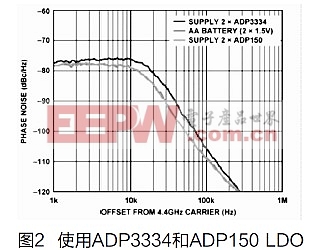

- 摘要:锁相环是现代通信系统的基本构建模块,而电源噪声越来越影响锁相环性能。本文通过列举多种电源管理电路设计的新方法,解析不同的设计对锁相环性能产生的影响。

- 关键字:

VCO PLL 201209

- 摘要:本设计基于DDS原理和FPGA技术按照顺序存储方式,将对正弦波、方波、三角波、锯齿波四种波形的取样数据依次全部存储在ROM波形表里,通过外接设备拨扭开关和键盘控制所需波形信号的输出,最终将波形信息显示在LC

- 关键字:

FPGA DDS 信号发生器

- 1引言高性能合成频率广泛应用在现代通信、雷达和电子测量等技术领域中。频率合成方法主要有3种...

- 关键字:

DDS PLL技术 高频时钟

- 1971年3月,美国学者J.Tierncy,C.M.Rader和B.Gold最先提出直接数字合成技术(DirectDigitalSynthesis),简称D...

- 关键字:

DDS 任意波形发生器 频率合成

- DDS同 DSP(数字信号处理)一样,是一项关键的数字化技术。DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广

- 关键字:

FPGA DDS 原理

- 在非相参雷达测试系统中,频率合成技术是其中的关键技术之一,它要求在一个很宽的频率范围内以快捷的速度,提供大...

- 关键字:

PLL 低相位噪声 环路滤波器

- 一般情况下,可以用一个现有的振荡器,为一个UART产生一个波特率时钟。振荡器频率必须作分频,而分频会带来波...

- 关键字:

DDS 波特率发生器 示波器

- XC25BS7系列是内置分频,倍频电路,在整个频率范围内保持低消耗电流,具有超小型封装的PLL时钟发生器IC。输...

- 关键字:

PLL 时钟发生器 XC25BS7

- 摘要:定时同步是高速数据传输的关键技术也是难点问题。在对锁相环数字化设计、DDS原理结构和参数设计进行研究的基础上,提出了一种基于DDS的高速定时同步方法,对该定时同步方法的原理结构框图进行了详细的论述,对

- 关键字:

同步 方法 定时 高速 DDS 基于

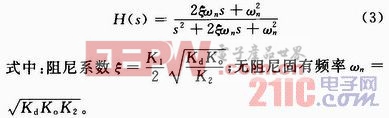

- 1 引言 本文在传统锁相环结构的基础上进行改进,设计了一款用于多路输出时钟缓冲器中的锁相环,其主 要结构包括分频器、鉴频鉴相器(PFD)、电荷泵、环路滤波器和压控振荡器(VCO)。在鉴相器前采用预 分频结构减小时

- 关键字:

CSMC PLL 工艺 零延时

- 新款ADF4159上的鉴频鉴相器最高工作频率可达110MHz,功耗低于100mW;内置高分辨率25位小数N分频模数和片内FMCW斜坡发生功能

全球领先的高性能信号处理解决方案供应商ADI最近推出业界性能最高的ADF415913GHzPLL频率合成器。ADF4159实现了突破性的110MHz鉴频鉴相器工作频率,同时功耗低于100mW,仅为竞争解决方案的五分之一。此外,ADF4159包含25位固定模数和产生高线性斜坡曲线的片内功能,使其非常适合频率调制连续波(FMCW)雷达应用,包括汽车雷达系统、微

- 关键字:

ADI 频率合成器 PLL

dds+pll介绍

您好,目前还没有人创建词条dds+pll!

欢迎您创建该词条,阐述对dds+pll的理解,并与今后在此搜索dds+pll的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473