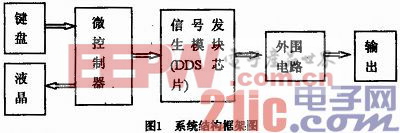

- 文章介绍了一种基于DDS的正弦信号发生器的设计方法,对此正弦信号发生器的硬件部分进行了详细的论述,并给出了系统的软件流程框图。仿真及硬件验证的结果表明,此正弦信号发生器精度高,抗干扰性好,可作为一般的正弦信号发生器使用。此设计方案具有一定的实用性。

- 关键字:

STC89C52 AD9850 正弦信号发生器 DDS

- Mouser Electronics备货由Analog Devices推出的业界最高频率PLL合成器。 ADI ADF41020微波PLL合成器旨在改善下一代无线电设计的性能,同时大幅减少元件数量并降低系统成本。

- 关键字:

ADI Mouser ADF41020 PLL

- 摘要 介绍了DDS的基本工作原理,阐述了DDS技术局限性,最终实现了一种基于FPGA+DDS可缡编程低相位噪声的频率源,输出信号范围170~228 MHz。测试结果表明,该频率源具有高频率分辨率和低相位噪声等特点,能够满足通信

- 关键字:

DDS 频率源

- 在此介绍了一种以DDS芯片AD9912作为信号源的高频石英晶体测试系统。AD9912是一款直接数字频率合成芯片。一方面,AD9912内部时钟速度可高迭1 GSPS,并集成了14位数/模转换器,可以直接输出400 MHz信号,另一方面,AD9912的频率控制字为48位,可以小于4 μHz的分辨率输出信号。由于采用了DDS芯片AD9912作为信号源,所设计的石英晶体测试系统能够在20kHz~400 MHz范围内测试石英晶体的串联谐振频率。与国内目前普遍使用的基于振荡器和阻抗计测试方法的测试仪相比,该测试

- 关键字:

DDS 高频 测试系统 石英晶体

- 锁相环(PLL)频率合成器中的电荷泵电压用于控制VCO的振荡频率。大多数PLL的电荷泵电压一般为5V或6V,因而电荷泵电压可控的VCO频率调谐范围和调谐精度都是有限的。ADI公司推出带高电压电荷泵的PLL频率合成器ADF4113HV

- 关键字:

合成器 设计 频率 PLL 电压 电荷 基于

- 摘要:常规DDS频率合成方案无法合成超过1/2采样频率的信号频率,这给DDS器件的应用带来了很大限制。在实际应用中通过对DDS器件的输出信号频谱进行分析发现,其频谱中除包含设计频率以外还包含特高频(UHF)频段的镜像

- 关键字:

DDS 镜像频率 AD9912 特高频信号

- DDS的基本原理是利用采样定理,通过查表法产生波形。DDS的结构有很多种,其基本的电路原理可用图3 来表示。 相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲FS,加法器将频率控制字K与累加寄存器输

- 关键字:

DDS 工作原理

- SOPC(System on a Programmable Chip,片上可编程系统)是Altera公司提出的一种灵活、高效的SOC解决方案。它将处理器、存储器、I/O接口、LVDS、CDR等系统设计需要的功能模块集成到一个可编程逻辑器件上,构建一个可

- 关键字:

Nios DDS IP核 可重构

- 在高可靠应用领域,如果设计得当,将不会存在类似于MCU的复位不可靠和PC可能跑飞等问题。CPLD/FPGA的高可靠性还表现在,几乎可将整个系统下载于同一芯片中,实现所谓片上系统,从而大大缩小了体积,易于管理和屏蔽。

- 关键字:

DDS 优化设计

- 摘 要:本文简要介绍DDS器件AD9858的系统结构和基本原理,以及使用AD9858实现复杂雷达信号源的原理和方法,并以AD9858产生二相码为例,说明了AD9858的基本特点和使用中应该注意的一些问题。关键词:复杂雷达信号源;二相

- 关键字:

9858 DDS AD 器件

- 与石英晶体振荡器等效的频率稳定的1~399KHZ PLL合成振荡电路电路的功能如果要求振荡频率准确、稳定度好, ...

- 关键字:

石英晶体 振荡器 频率稳定 PLL

- 本文介绍了一种利用LC 谐振原理测量电容自身寄生电感的方法。利用直接数字合成器产生可编程的扫频信号激励 ...

- 关键字:

DDS 扫频技术 电感测量仪

- 1 引言由于传统的多波形函数信号发生器需采用大量分离元件才能实现,且设计复杂,这里提出一种基于CPLD的多波形函数信号发生器。它采用CPLD作为函数信号发生器的处理器,以单片机和CPLD为核心,辅以必要的模拟和数字

- 关键字:

CPLD DDS 信号源 滤波器

- 新一代的直接数字频率合成器DDS,采用全数字的方式实现频率合成。与传统的频率合成技术相比DDS具有以下特点:(1)频率转换快。直接数字频率合成是一个开环系统,无任何反馈环节,其频率转换时间主要由频率控制字状态改

- 关键字:

DDS 数字频率合成器 优化设计

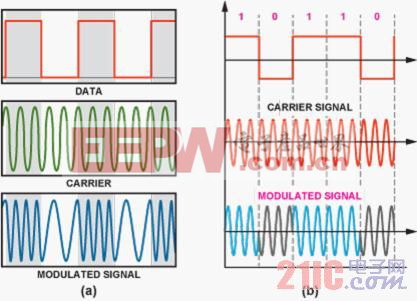

- 频移键控 (FSK)和相移键控 (PSK) 调制方案广泛用于数字通信、雷达、RFID以及多种其他应用。最简单的FSK利用两个离散频率来传输二进制信息,其中,逻辑1代表传号频率,逻辑0代表空号频率。最简单的PSK为二进制(BPSK)

- 关键字:

DDS 实现 切换 通道 利用 FSK/PSK 调制器 高效

dds+pll介绍

您好,目前还没有人创建词条dds+pll!

欢迎您创建该词条,阐述对dds+pll的理解,并与今后在此搜索dds+pll的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473