- 摘要:基于新一代图像压缩国际标准JPEG 2000,介绍一种快速、有效的多层5/3小渡变换的VLSI设计结构,该方法使用两组一维变换实现,用移位-相加代替乘法操作,整体设计采用了流水线设计。利用双端口RAM和地址生成模块

- 关键字:

JPEG 2000 FPGA 离散小波

- 摘要:针对Xilinx FPGA在航天应用中的可行性,文章分析了Xilinx FPGA的结构以及空间辐射效应对FPGA的影响,结合实际工程实践给出了提高其可靠性的一有用办法和注意事项,如冗余设计、同步设计、自检等。表明配置信息

- 关键字:

Xilinx FPGA 辐射 设计技术

- 摘要:文章从FPGA逻辑编程设计技术、EMC技术、高速电路PCB设计技术等几个方面介绍了时统接收处理模块的抗干扰设计及其实现方法,实现了同步脉冲的提取、对时功能、自守时、脉宽调制等功能,提高了同步精度和抗干扰性

- 关键字:

FPGA 模块 可靠性设计

- 摘要:出租车计费系统大多利用单片机进行控制,较易被改装,且故障率较高。针对这一问题,设计了一种基于FPGA的出租车计费系统,可模拟汽车行驶、暂停等待,停止等过程,并可同时显示金额、乘车总路程。设计采用层次

- 关键字:

FPGA 出租车 计费 系统设计

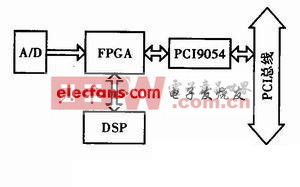

- 本文设计的系统采用PLX公司生产的CPCI协议转换芯片PCI9054,通过Verilog HDL语言在FPGA中产生相应的控制信号,完成对数据的快速读写,从而实现了与CPCI总线的高速数据通信。高速数据传输技术是现代信息技术的前沿科技

- 关键字:

数据通信 CPCI 实现 FPGA 基于

- 摘要:以ADS8341为例,介绍了基于FPGA使用串行输出A/D转换器实现对多通道准同步采样的方法,逻辑控制方式FPGA相比程序流程式的单片机而言,运行更为可靠,通过时序仿真和试验验证了该控制方法的正确性,系统体积小、

- 关键字:

记录仪 应用 数据 微型 FPGA 串行

- 摘要:根据工业应用的实际需要以及网络通信发展的功能要求,提出了基于FPGA智能变送器控制系统的总体方案,设计了以XILINX公司的Spartan3系列XC3S4005PO208C可编程逻辑器件为主控制器、DM9000A为以太网通信接口、SJA

- 关键字:

FPGA 智能变送器

- 该便携式接触网故障信号分析仪采用图形化程序设计语言LabVIEW开发设计, 可实现数据的高速实时采集、在线分析、自动存储、显示等功能。高速数字化仪NI PXI- 5112卡采样速度高、性能稳定可靠, 适宜对高速变化信号的实时监测。将软件安装在PXI- 1042工控机上, 具有体积小、抗干扰能力强、携带方便等特点, 同时具有故障性质判断、故障定位功能。该系统目前已经在石家庄变电所现场运行, 效果良好。

- 关键字:

FPGA 8051 TCP IP

- 本设计的主要创新点在于 USB总线的协议的复杂性和快速性为设计实现必须面对许多的挑战,能在分析协议的基础上利用 CPLD解决了 USB总线隔离的问题,巧妙的检测信息包起始、快切换和包结束的难题,克服了传输信息包结束慢上拉与过渡,保证系统的完整性。

- 关键字:

CPLD USB 总线 隔离接口

- 摘要 在分析Sony公司ICX098BQ面阵CCD图像传感器驱动时序的基础上,对可调节曝光时间的CCD时序发生器及其硬件电路进行设计。选用FPGA器件作为硬件设计平台,使用VHDL语言对时序关系进行了硬件描述。采用QuartusII 8.0

- 关键字:

FPGA CCD 面阵 发生器

- 随着通信与网络技术的不断发展,使我国用现有的E1资源来传输以太网业务成为广泛的应用。以太网数据要通过E1线路传输就必须对以太网净荷数据进行帧封装,才能从E1线路上恢复出以太网数据帧,完成以太网数据的交换。通常,以太网数据是通过HDLC协议或GFP协议来进行封装的。本文介绍了中国移动标准协议转换器中以太网到单路E1转换器HDLC协议封装的FPGA(现场可编程逻辑阵列)设计与实现。

- 关键字:

中国移动 FPGA 201106

- 摘要 基于Flash存储器的Hamming编码原理,在Altera QuartusⅡ7.0开发环境下,实现ECC校验功能。测试结果表明,该程序可实现每256 Byte数据生成3 Byte的ECC校验数据,能够检测出1 bit错误和2 bit错误,对于1 bit错误

- 关键字:

Flash FPGA NAND ECC

- 随着半导体工艺技术的迅猛发展,现场可编程逻辑器件FPGA的集成度迅速提高,已达到百万门量级,与此同时,FPGA中的逻 ...

- 关键字:

ARM FPGA 加载配置

- 摘要:提出一种通过两个二阶节级联构成四阶IIR数字椭圆滤波器的设计方法,并利用Matlab仿真软件设计了通带内波纹不大于0.1 dB,阻带衰减不小于42 dB的IIR数字滤波器。论述了一种采用可编程逻辑器件,通过VHDL硬件描

- 关键字:

Matlab FPGA IIR 数字滤波器

cpld/fpga介绍

您好,目前还没有人创建词条cpld/fpga!

欢迎您创建该词条,阐述对cpld/fpga的理解,并与今后在此搜索cpld/fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473