- 在现代数字通信中,对数据传输容量和传输效率的要求越来越高,因此经常依据时分复用[1]的原理通过数字复接与分...

- 关键字:

数字复接技术 FPGA 时分复用

- 摘要:在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。

- 关键字:

FPGA 时钟设计

- 1 引 言 在雷达及声纳信号处理系统中,波束形成算法通常采用DSP软件编程实现,控制逻辑电路采用CPLD来完成,这种方法具有软件编程灵活、功能易于扩展的优点,但对于实时性能要求很高的系统,如雷达、声纳探测和

- 关键字:

FPGA 自适应波束 算法

- 针对高清图像在中值滤波预处理过程中排序量多、速度慢的特点,提出适合邻域图像并行处理机的分块存储方法。在流水线结构下,1个时钟周期可以并行处理32个3×3邻域的中值滤波运算,实现了高速、实时的1 920×1 080灰度图像中值滤波器。

- 关键字:

FPGA 中值滤波 硬件实现

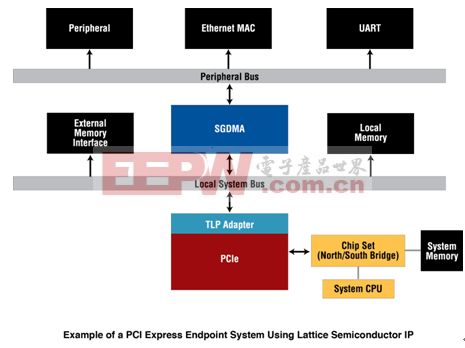

- 莱迪思半导体公司日前宣布LatticeECP3TMFPGA系列符合PCI Express 2.0在2.5Gbps的规范。针对最近PCI – SIG研讨会上涉及的1-通道和 4-通道配置,LatticeECP3 FPGA和其PCI Express(PCIe)IP核通过了符合PCI - SIGPCIe 2.0规范和互操作性的测试,确保莱迪思的解决方案与现有的支持系统的PCIe 2.0具有互操作性。

- 关键字:

莱迪思 FPGA

- 全球可编程平台领导厂商赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布荣膺中国经济CEO论坛“2011中国经济-最佳推动力企业”奖。赛灵思公司全球高级副总裁、亚太地区执行总裁汤立人(Vincent Tong)和亚太地区销售与市场副总裁杨飞先生,出席了由东方企业家、经理人杂志、新民周刊、金融界、北京电视台、香港科技大学商学院、中国企业国际发展协会联合在北京发起主办的 “中国经济CEO论坛暨中国经济成就奖评选颁奖盛典”。 商务部国际贸易经济合作研究院研究员白明代表中国经济CEO 论坛

- 关键字:

赛灵思 FPGA

- 莱迪思半导体公司(NASDAQ: LSCC)今日宣布LatticeECP3TMFPGA系列符合PCI Express 2.0在2.5Gbps的规范。针对最近PCI – SIG研讨会上涉及的1-通道和 4-通道配置,LatticeECP3 FPGA和其PCI Express(PCIe)IP核通过了符合PCI - SIGPCIe 2.0规范和互操作性的测试,确保莱迪思的解决方案与现有的支持系统的PCIe 2.0具有互操作性。

- 关键字:

莱迪思半导体 FPGA

- 1.引言随着电子技术的发展,复杂可编程逻辑器件CPLD(ComplexProgrammableLogicDevice)以其高速、高...

- 关键字:

CPLD 线缆快速测试

- 上个月接到任务,要求设计一视频钻孔机,用摄像头检测孔位,脚踏开关控制电机钻孔。由于要对准孔位,因此显示器上要...

- 关键字:

LM1881 CPLD 电视

- 0引言传统的数据采集系统一般采用单片机,系统大多通过PCI总线完成数据的传输。其缺点是数学运算能力差...

- 关键字:

CPLD FPGA 数据采集系统

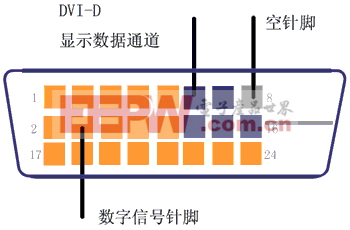

- 一种基于FPGA控制全彩大屏幕显示的设计,随着数字技术的飞速发展,各种数字显示屏也随即涌现出来有LED、LCD、DLP等,各种数字大屏幕的控制系统多种多样,有用ARM+FPGA脱机控制系统,也有用PC+DVI接口解码芯片+FPGA芯片联机控制系统,在这里我们讲述一种不仅

- 关键字:

显示 设计 大屏幕 全彩 FPGA 控制 基于

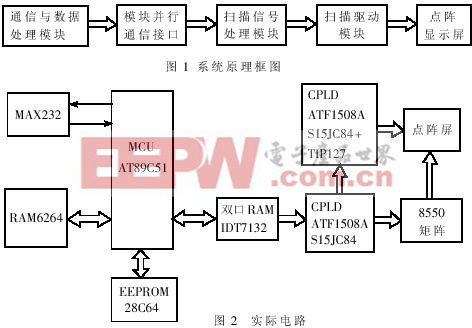

- 基于CPLD和Embedded System的LED点阵显示,摘要:采用自顶向下的设计思想,综合运用EDA 技术、CPLD技术和共享式双口RAM,解决了大屏幕LED点阵显示屏无闪烁显示的技术难题。给出了系统设计方法及实际电路。LED点阵显示屏是显示公共信息的一种重要显示终端,其中

- 关键字:

点阵 显示 LED System CPLD Embedded 基于

- FPGA器件的在线配置方法,摘要:介绍基于SRAM LUT结构的FPGA器件的上电配置方式;着重介绍采用计算机串口下载配置数据的方法和AT89C2051单片机、串行EEPROM组成的串行配置系统的设计方法及实现多任务电路结构中配置的方法,并从系统的复杂度、

- 关键字:

方法 配置 在线 器件 FPGA

- 摘要:采用FPGA实现四阶IIR数字滤波器,通过两个二阶节级联构成数字椭圆低通滤波器。通带内波纹小于0.1dB,阻带衰减大于32dB。 常用的数字滤波器有FIR数字滤波器和IIR数字滤波器。FIR数字滤波器具有精

- 关键字:

滤波器 数字 IIR FPGA 基于

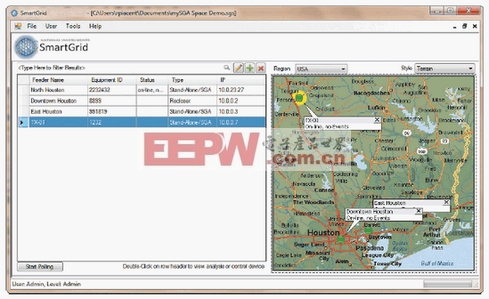

- 我们生活的方方面面越来越受新技术的影响——从我们手中的电话到我们的阅读方式。

整个工业界都在向数字领域转变——一个涵盖了软件,网络,处理器,以及传感器的融合与信息交换的信息技术(IT)新世界。

是什么使这种改变如此不可抗拒,看起来没有任何行业能够阻止它的脚步?这当中有很多原因,从快速的物流和服务,到巨大的生产力。无论如何,最重要的还是性价比。事实证明,信息技术带

- 关键字:

NI 嵌入式系统 FPGA

cpld/fpga介绍

您好,目前还没有人创建词条cpld/fpga!

欢迎您创建该词条,阐述对cpld/fpga的理解,并与今后在此搜索cpld/fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473