arm cortex-x5 ipc 文章

最新资讯

- 北京时间3月9日凌晨消息,彭博社日前发表文章称,微软将在其Azure云服务服务器上使用ARM芯片,这可能威胁英特尔在数据中心处理器市场的长期主导地位。

去年年底,微软已经与高通合作,推出了基于ARM处理器的完整版Windows 10系统。而微软Azure云业务副总裁詹森·桑德(Jason Zander)日前表示,微软正在测试ARM芯片,将其应用到搜索、存储、机器学习和大数据等领域。

到目前为止,微软尚未在面向消费者的网络上使用ARM处理器,也并未说明将来会在多大范围内使用AR

- 关键字:

ARM Azure

- 北京时间3月8日消息,据外媒报道,知情人士称,在主要投资者想要将芯片厂商ARM控股纳入他们的投资组合后,软银集团计划将ARM的25%股份出售给一家科技基金。该基金由软银与沙特联合创建。

知情人士称,软银将以80亿美元出售这部分ARM股份。这笔交易并不属于软银此前承诺向愿景基金(Vision Fund)投资250亿美元的一部分。

软银创始人孙正义(Masayoshi Son)正与沙特、阿布扎比穆巴达拉发展公司以及其他投资者建立一只规模为1000亿美元的投资基金,该基金将会使得孙正义成为全球最

- 关键字:

软银 ARM

- 随着物联网时代的到来,已不在是未来概念,引领信息科技与传统领域融合,且还能带动数十万亿美元的经济价值,无论是IBM、ARM和英特尔等国际巨头,还是华为、BAT等为代表都已瞄准物联网,能充分利用物联网的企业将会成为万物互联时代的赢家,那么在2017年,在物联网领域有哪些最值得关注的公司?

谷歌

谷歌自2014年以32亿美元收购Nest智能家居厂商,正式踏入物联网领域,在长期关注物联网发展的杨剑勇先生看来,由于这一笔交易,也促使了众多科技企业纷纷开始涉足智能家居领域。尽管Nest没有达到预

- 关键字:

物联网 ARM

- 未来30年,中国最重要的机遇是什么?我们认为是制造业的科技升级。但真正让制造业科技升级的并不是如何造,而是造什么,是如何跟世界最先进的科技研发来对接。

- 关键字:

ARM iPhone

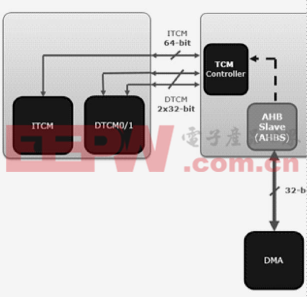

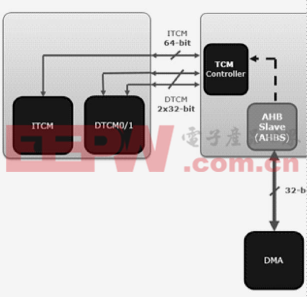

- 对于那些需要低功耗、成本效益和中等性能的嵌入式系统而言,ARM Cortex M系列无疑是首选的处理器系列。 Cortex M系列中最早得到应用的是其光谱中的小部分产品: Cortex M0用于实现最低的成本,Cortex M0+用于实现最高 的能效,Cortex M3用于实现功耗与性能之间的最佳平衡, Cortex M4用于实现那些需要数字信号处理(DSP)功能的应 用。 该系列中最高性能的Cortex M7的首批应用现已开

- 关键字:

Cortex M7 内存

- 据金融时报报道,据透露,日本软银公司将把ARM 25%的股权出售给它创立的1000亿美元投资基金Vision Fund。该部分股权价值大约80亿美元。

据两位知情人士透露,该决定正值该软银领投的基金寻求达到它的融资目标,获得阿布扎比政府资助的投资集团Mubadala的支持。据称,Mubadala希望该基金拥有ARM的部分股权。

知情人士称,双方正接近达成协议,Mubadala拟向该基金注资150亿美元,帮助软银更加接近于实现为Vision Fund基金完成1000亿美元融资的目标。

- 关键字:

软银 ARM

- 因为投资阿里巴巴的远见而被国人津津乐道的孙正义,如今正将全部的注意力投向人工智能,也就是AI。

近日的世界移动通讯大会(MWC)上,日本软银总裁孙正义发表演讲,首次披露了他去年收购英国芯片架构厂商ARM后的最新进展,以及他为何要领投OneWeb这家从事生产、发射卫星的美国公司。

孙正义志在将ARM打造为未来智能界具有垄断地位的公司,他预言明年人工智能的“奇点”就会到来,穿上安装芯片的鞋子,脚可以比脑袋更聪明。

“你脑袋的智商可能还不如脚&rdquo

- 关键字:

ARM 人工智能

- 3月1日消息,据美国媒体报道,尽管过去几年比较糟糕,但今年晚些时候Windows PC将依靠ARM芯片回归,只是只有高通芯片。另一家重要的ARM芯片制造商联发科(MediaTek)并未争取将ARM芯片安装到Windows PC的机会,因为该公司认为这种机会有限。

联发科的芯片已经使用到Chromebook中,但ARM在Windows中的应用历史比较糟糕,这是该公司置身局外的另一个原因。ARM进入PC的情况如同英特尔试图打入智能手机市场一样--联发科的销售总经理分巴尔·莫伊尼翰(Fi

- 关键字:

高通 ARM

- 随着网络速度的提升与普及,低价位、续航时间长的上网本愈来愈受到消费者的青睐。ARM架构的上网本以其体积小、重量轻、成本低、功耗小、持久续航力、生产和维护简单而受到很多生产厂商和消费者的瞩目。飞思卡尔(Freescale)、德州仪器(TI, Texas Instrument)、安凯(Anyka)、三星(Samsung)等公司基于ARM架构的处理器逐步占据一定市场。ARM架构的上网本通常用两节或三节锂电供电,通过高效率降压DCDC转换成5V电压,再由5V电压转换成3.3V、2.5V、1

- 关键字:

AP2953 ARM

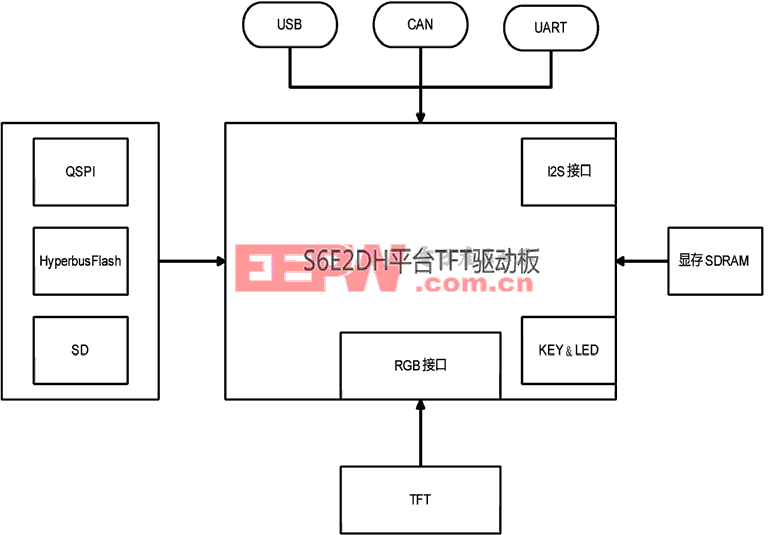

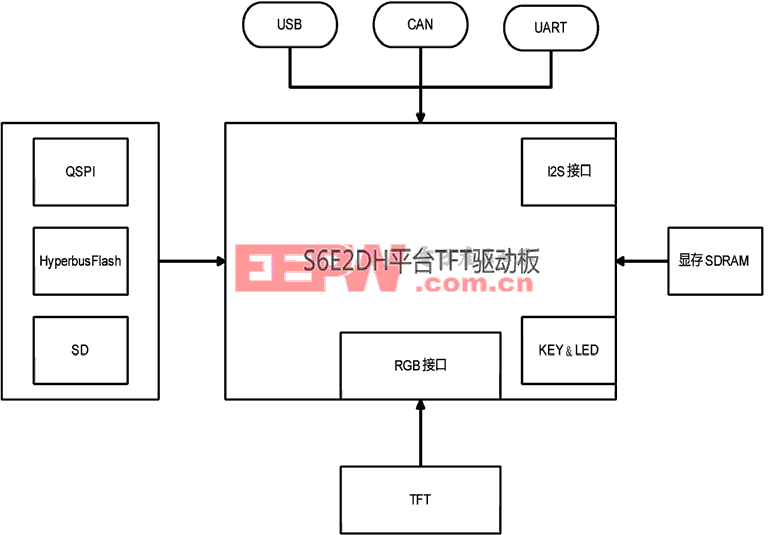

- 引言 目前在物联网相关应用中,包括使能家具显示面板、 工控显示面板、手持设备、人脸识别等领域都在逐步由传统 的黑白点阵LCD或者段式LCD显示向彩色TFT屏显示发展, 主要是因为彩色TFT屏幕显示内容丰富而且价格也越来越便 宜,但是基于彩色TFT的显示面板大都显示内容复 杂,效果多,素材占用资源大,这就对微处理器的 处理能力提出了更高的要求,现在大多数的方案都 是基于ARM9、A8或者更高端的处理器去实现相关 功能,这些方案实现起来开发复杂,开发周期长, BOM成本

- 关键字:

Cypress Cortex-M4 显示

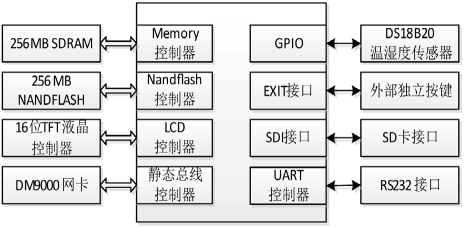

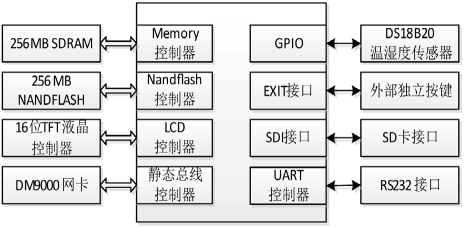

- 引言测温测量和控制在当今社会生活中扮演着至关重要的 角色,国际国内市场现有的多种测温技术涵盖了安检、市 场、生活、消防、科研等诸多领域。温度的测量和控制在工 业生产中有广泛的应用,尤其在石油、化工、电力、冶金等 重要工业领域中,对温度的测量和监控是非常重要的一个环 节。在传统的温度测量系统中,温度采集器通常采用模拟温 度传感器,模拟信号在传输的过程中容易受到干扰从而影响 测量的准确度,模拟信号转化成数字信号,精度较高的A/D 转换器一般价格昂贵,对于传统系统存在的不足,结合国内 外在温度监测系统上的研究现

- 关键字:

ARM 智能测温系统

- 由ARM与厚朴投资共同管理的厚安创新基金 (HOPU-ARM Innovation Fund)日前正式启动。该基金的投资者包括中国主权财富基金、中国政府机构下设基金、深圳市政府全资公司以及国际知名投资机构。

结合ARM的全球产业生态系统和厚朴投资丰富的投资经验,厚安创新基金致力于投资来自ARM中国及全球生态系统中极具潜力的技术公司,覆盖一系列创业、创新投资项目,加速以物联网、智能硬件、云计算、大数据、人工智能等为代表的关键性创新应用的诞生。

ARM一直以来与中国共同成长,并积极推动中国创新

- 关键字:

ARM 芯片

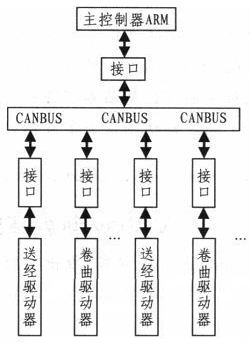

- 引 言 在电气智能化发展无处不在的今天, 无数用电场合离不开逆变电源系统( Inverted Pow er Supply System,IPS) 为现场设备提供稳定的高质量电源, 特别在如通信机房、服务器工作站、交通枢纽调度中心、医院、电力、工矿企业等对电源保障有苛刻要求的场合。许多IPS产品因遵循传统设计而不符合或落后于现代电源理念,突出表现为控制模块的单一复杂化, 控制器芯片落后且控制任务繁重,&

- 关键字:

ARM DSP

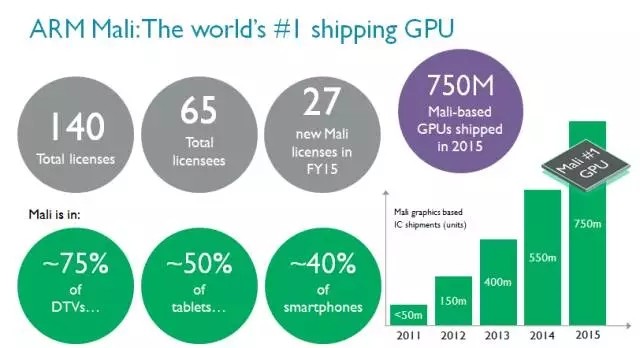

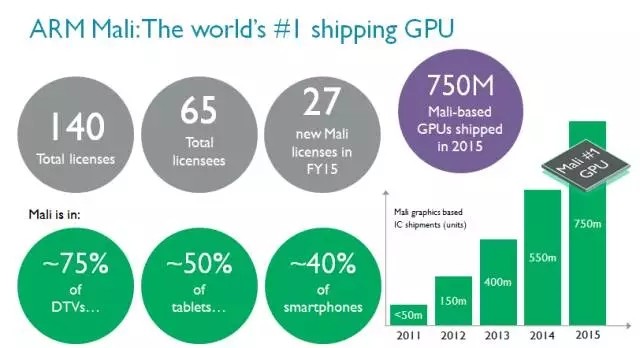

- GPU性能从2011年到2016年提升了20倍,GPU爆炸式发展背后的深层原因是什么?基于GPU技术发展有哪些最新的案例应用呢?智能手机设计的挑战与趋势又是什么?且听ARM技术专家娓娓道来。

- 关键字:

GPU ARM

- 根据全球领先的信息技术研究和顾问公司Gartner最新研究结果,中国国有企业将成为全球最活跃的投资者,竭力在增长缓慢的半导体市场内跻身为世界级厂商。因此,各半导体企业技术业务部的领导者们应针对未来在华业务制定新计划。

Gartner对于半导体投资市场的预测具体如下:

1000多亿美元的投资将令中国本土半导体企业的营收到2025年提升3倍

中国政府拥有强大的力量,以引导国内资本重点流向由国有或国家持股公司所运营的特定行业。对于需大规模投资的行业(如:LCD面板、高速铁路、太阳能和LED

- 关键字:

ARM X86

arm cortex-x5 ipc介绍

您好,目前还没有人创建词条arm cortex-x5 ipc!

欢迎您创建该词条,阐述对arm cortex-x5 ipc的理解,并与今后在此搜索arm cortex-x5 ipc的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473