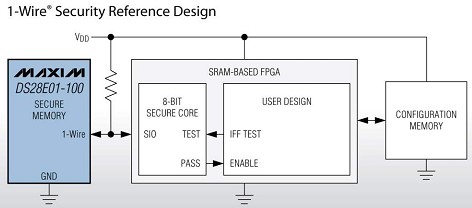

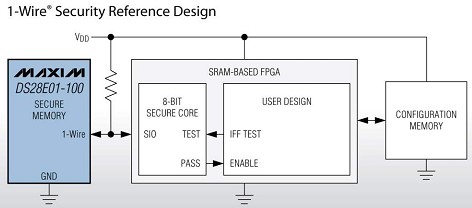

- Maxim Integrated Products, Inc. (NASDAQ:MXIM)推出用于保护Xilinx® Spartan®-6现场可编程门阵列(FPGA)的参考设计,其中包括Maxim或Xilinx免费提供的安全保护软件和Maxim®的1-Wire®安全存储器DS28E01-100。

- 关键字:

Maxim FPGA DS28E01-100

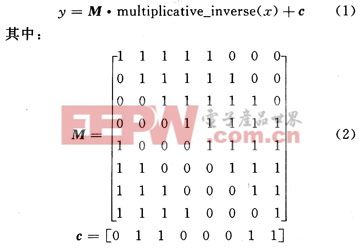

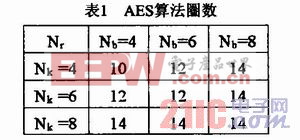

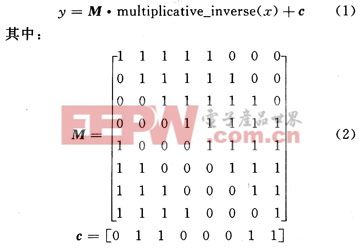

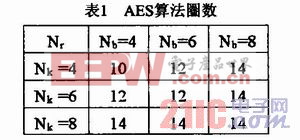

- 摘要 AES是美国高级加密标准算法,将在未来几十年里代替DES在各个领域中得到广泛应用。本文在研究分析AES加密算法原理的基础上,着重说明算法的实现步骤,并结合AVR汇编语言完整地实现AES加密和解密。根据AES原理,提出几

- 关键字:

及其 优化 AES 实现 汇编语言 AVR

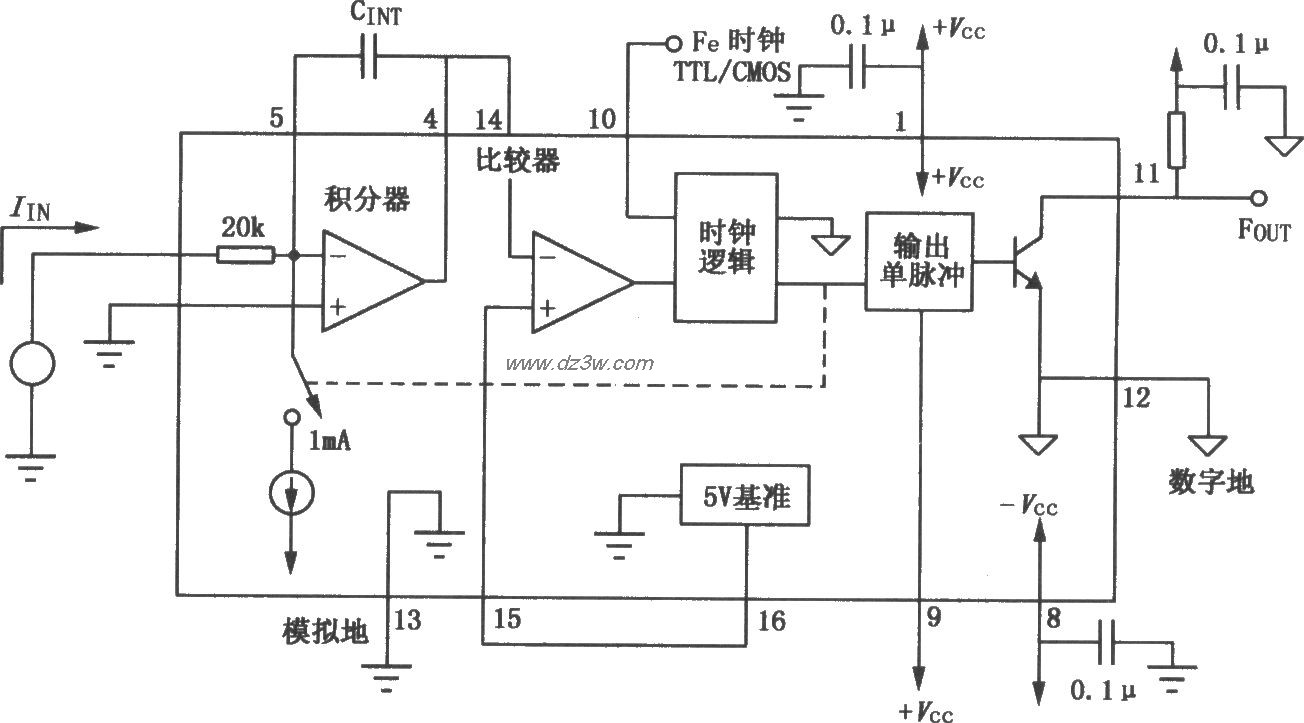

- IIN/C1(V/S),1UA电流为10的负6次方/800*10的负12次方=1.25*10的6次方V/S,穿越-5.6~+5.6V的时间林约是9MS,频率为111HZ。实际上必须加上上升时间,所以振荡频率大约为100HZ。 因为C1的微调很困难,所以允许A2的正

- 关键字:

100 0.1 KHZ NA

- AES算法中S-box和列混合单元的优化,1 S-box的优化设计

在AES标准算法中定义了两个较大的列表。S-box和逆S-box。将S-box用于两个应用:字节替代和密钥扩展。而逆S-box则用于逆字节替代。这两个列表是不相同的,因此必须建立两个不同的ROM(256times;

- 关键字:

单元 优化 混合 S-box 算法 AES

- 电路的功能高速A-D转换器采用快捷式,但由于输入电阻小,所以必须加缓冲放大器。本电路是一种适用于放大高速脉冲信号的超宽带放大器。CLC221A芯片性能良好,转换速度为6500V/US、TR=TF=2.1NS,-3DB带宽为170MHZ,失调

- 关键字:

100 MHZ 带宽 超宽带

- 电路的功能高速A-D转换器采用快捷式,但由于输入电阻小,所以必须加缓冲放大器。本电路是一种适用于放大高速脉冲信号的超宽带放大器。CLC221A芯片性能良好,转换速度为6500V/US、TR=TF=2.1NS,-3DB带宽为170MHZ,失调

- 关键字:

100 MHZ 带宽 超宽带

- 1 引言 美国Atmel公司生产的AT94K系列芯片是以Atmel0.35的5层金属CMOS工艺制造。它基于SRAM的FPGA、高性能准外设的Atmel8位RISCAVR单片机。另外器件中还包括扩展数据和程序SRAM及器件控制和管理逻辑。图1-1是Atme

- 关键字:

解密 分组 设计 AES 基于 DES FPSLIC

- 摘要 针对高温温度计存在体积大、成本高、操作复杂及实际测量依赖电脑而不能独立工作等缺点,研究了温度数据的采集、传输、显示等问题,设计出以STC89C52为核心,基于Pt100温度传感器和液晶1602显示的铂电阻高温温度

- 关键字:

100 Pt 查表法 温度计

- 1 引 言

AES算法是由美国国家标准和技术研究所(NIST)用时3年,历经2轮评估,选出的高级加密算法。AES的所有设计原则都是公开的,没有专利权方面的问题,任何人都可以通过正常渠道得到并使用这种算法。作为新一代的

- 关键字:

应用 研究 机顶盒 PVR 算法 AES

- 摘要:近几年图形处理器GPU的通用计算能力发展迅速,现在已经发展成为具有巨大并行运算能力的多核处理器,而CUDA架构的推出突破了传统GPU开发方式的束缚,把GPU巨大的通用计算能力解放了出来。本文利用GPU来加速AES算

- 关键字:

实现 算法 AES GPU 基于

- 提出一种采用三级流水线型结构的9位100 MSPS折叠式A/D转换器,具体分析了其内部结构。电路使用0.6μm Bipolar工艺实现,由5 V/3.3V双电源供电,经优化设计后,实现了9位精度。100MSPS的转换速度,功耗为650mW,差分输入范围2.2V。给出了在Cadence Spectre的仿真结果,讨论了流水线A/D转换器设计的关键问题。

- 关键字:

MSPS 100 D转换 流水线结构

- 提出了一种高安全、高效率、低成本USB接口密钥的设计方法。采用8位USB微控制器MC9S08JS16,通过其内置的全速USB2.0模块,实现与PC机的通信,并采用现在公认最安全和高效的高级加密标准(AES)算法对输入数据进行加密,同时对AES在单片机中的加密程序进行了优化。实验表明,USB密钥可在短时间内完成对少量数据的加密,适用于加密数据量较小的场合,电路设计简单,稳定性高,易于携带。

- 关键字:

AES Key MC9 S08

- 介绍了一种适用于较小面积应用场合AES密码算法的实现方案。结合该算法的特点,在常规轮变换中提出一种加/解密列混合变换集成化的硬件结构设计,通过选择使用同一个模块,可以实现加密和解密中的线性变换,既整合了部分加/解密硬件结构,又节约了大量的硬件资源。仿真与综合结果表明,加/解密运算模块面积不超过25 000个等效门,有效地减小了硬件实现面积,同时该设计方案也满足实际应用性能的需求。

- 关键字:

AES 密码算法 硬件实现

aes-100介绍

您好,目前还没有人创建词条aes-100!

欢迎您创建该词条,阐述对aes-100的理解,并与今后在此搜索aes-100的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473