麻省理工学院和其他地方的研究人员开发了一种新的制造工艺,将高性能 GaN 晶体管集成到标准硅 CMOS 芯片上来自麻省理工学院网站:他们的方法包括在 GaN 芯片表面构建许多微小的晶体管,切出每个单独的晶体管,然后使用低温工艺将所需数量的晶体管键合到硅芯片上,以保持两种材料的功能。由于芯片中只添加了少量的 GaN 材料,因此成本仍然很低,但由此产生的器件可以从紧凑的高速晶体管中获得显著的性能提升。此外,通过将 GaN 电路分离成可以分布在硅芯片上的分立晶体管,新技术能够降低整个系统的温度。研究人员使用这种

关键字:

3D芯片 电子设备 GaN

上周,IEEE电子元件与技术会议(ECTC)的研究人员推动了一项对尖端处理器和存储器至关重要的技术。该技术被称为混合键合,将两个或多个芯片堆叠在同一封装中,使芯片制造商能够增加其处理器和存储器中的晶体管数量,尽管曾经定义摩尔定律的传统晶体管收缩速度普遍放缓。来自主要芯片制造商和大学的研究小组展示了各种艰苦奋斗的改进,包括应用材料公司、Imec、英特尔和索尼在内的一些研究小组显示的结果可能导致3D堆叠芯片之间的连接密度达到创纪录的密度,即在一平方毫米的硅中约有700万个链接。Imec设法在每2微米放置一次的

关键字:

混合键合 3D芯片

随着半导体先进制程持续往5奈米、3奈米逼近的同时,摩尔定律也正逐渐走向物理极限。制程的微缩不只越来越困难,耗用的时间也越来越长,成本也越走越高。这使得半导体也必须从材料端与封装端来打破制程技术的限制,并达到技术上的突破。也由于台湾的半导体实力在全世界有目共睹,这使得默克决定在台湾高雄成立其亚洲地区集成电路材料应用研究与开发中心。

默克研发中心的重点领域,包括用于薄膜制程的CVD/ALD材料,和用于后段封装连接和黏晶的导电胶。默克对此研发中心的投资超过280万欧元(约1亿新台币),此研发中心同时与

关键字:

3D芯片 摩尔定律

封装技术的进步推动了三维(3D)集成系统的发展。3D集成系统可能对基于标准封装集成技术系统的性能、电源、功能密度和外形尺寸带来显著改善。虽然这些高度集成系统的设计和测试要求仍在不断变化,但很显然先进的测试自

关键字:

3D芯片 测试 堆叠

电子系统层级(ESL)和高阶合成(HLS)方案试图以硬体取代软件。法新社在过去,由于软件内容不多、产品制备不容易延滞,开发业者会先设计硬体,再完成软件设计。时至今日,软件内容大增,软件设计逐渐比硬体占更多时间与成本,且是产品功能重要实现关键。

软件功能受到重视之甚,使得硬体开始被视为支援软件最佳化之平台。现在许多开发业者会先设计软件,并依据成本、功耗、存储器容量、体积等软件效能限制,去建造支援该软件的硬体设计。

软、硬体不只是技术层面需要顾及,还牵涉到公司结构问题,传统公司部门分化根深蒂固

关键字:

台积电 3D芯片

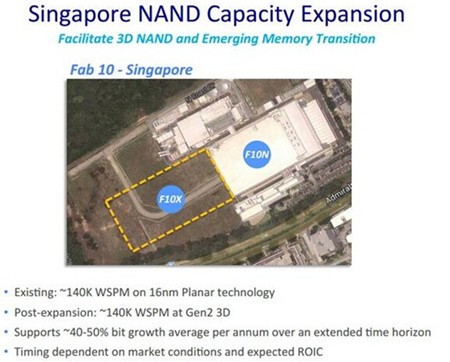

传统的平面闪存在16/15nm工艺之后面临瓶颈,厂商开始转向3D闪存,这其中三星动作最快,去年就已经开始量产第二代V-NAND闪存了,850 Pro及850 Evo硬盘也上市了。东芝/闪迪系也在跟进,在日本扩建Fab 2工厂准备3D闪存生产,Intel/美光系去年底也公开了他们的3D NAND闪存,现在也准备量产了。日前美光宣布投资40亿美元扩建新加坡的Fab 10晶圆厂,明年底开始量产第二代3D NAND闪存。

美光斥资40亿美元升级Fab 10X晶圆厂生产3D N

关键字:

美光 3D芯片

用光精确地控制神经元可以在脑科学研究和脑疾病治疗方面掀起一场革命。

光遗传学把光敏基因和光源结合在一起,用来选择性地打开或关闭大脑。光遗传学已经成为有希望的研究工具和潜在疗法。不过,这一技术大部分时候只把光打到某个点上,而脑部活动经常包括不同区域以复杂的顺序被激活。一个新的设备可以让光遗传学变成三维技术,把光的模式发送到脑部不同坐标的神经元上。

“在接下来的几年里,会出现大量的类似设备,”布朗大学纳米光学和神经工程实验室(Nanophotonics and Neur

关键字:

3D芯片 脑神经

4月18日消息,据路透社报道,三星电子周五表示,公司已将最新的芯片制造技术授权给美国制造商GlobalFoundries。此举旨在帮助后者改善生产力,以提高其在面对像苹果这样的大订单时与台积电的竞争力。

GlobalFoundries是全球第二大合同芯片制造商。而根据周五公布的声明,该公司如今已从三星获得了3D芯片制造工艺的授权,或称为FinFET。

三星已计划在今年第四季度展开14纳米工艺的FinFET量产。公司希望不断提高产能,以满足当前日趋增加的市场需求。

3D晶体管比传统平面

关键字:

GlobalFoundries 3D芯片

美商陆得斯科技(RudolphTechnologies,Inc.)指出,到了3D晶片时代,矽钻孔(TSV)、微凸块(microbumping)等半导体制程技术越趋复杂,每一道程式的精密控制均开出新的检测需求,预料光学检测设备扮演角色依旧吃重,甚至将自表面量测等现行主流用途,开展出更大应用空间。

光学检测作为制程式控制制(processcontrol)的重要环节,无论是在半导体前段抑或后段制程,都扮演着决定成品可靠度的重要关键。随着3D晶片时代箭在弦上,不仅晶片尺寸缩微,制程也更加精密,自动光

关键字:

3D芯片 光学检测

来自全球11个国家、超过200位的半导体封装技术专家,近日齐聚一堂探讨能有助于维持半导体技术创新步伐的中介层(interposer)与IC封装技术;专家们的结论是, 3D晶片堆叠技术已经准备就绪,但有需要再进一步降低成本。

由美国乔治亚理工大学(Georgia Tech)封装研究中心(Packaging Research Center,PRC)所主办的第三届年度中介层技术研讨会上,来自Amkor、日月光(ASE)等半导体封装大厂的专家明确指出,他们已经准备好为以中介层基础的设计进行封装与测试;此

关键字:

3D芯片 封测

来自全球11个国家、超过200位的半导体封装技术专家,近日齐聚一堂探讨能有助于维持半导体技术创新步伐的中介层(interposer)与IC封装技术;专家们的结论是,3D晶片堆叠技术已经准备就绪,但有需要再进一步降低成本。

由美国乔治亚理工大学(GeorgiaTech)封装研究中心(PackagingResearchCenter,PRC)所主办的第三届年度中介层技术研讨会上,来自Amkor、日月光(ASE)等半导体封装大厂的专家明确指出,他们已经准备好为以中介层基础的设计进行封装与测试;此外晶圆代

关键字:

3D芯片 封测

台积电、日月光、矽品等大厂积极架构2.5D及3DIC封测产能,一般预料明年将进入3DIC量产元年,启动高阶生产线及3DIC设备商机,国内主要设备供应商弘塑、辛耘及万润等业绩吃香。

设备厂表示,3DIC可以改善存储器产品的性能表现与可靠度,并可协助减低成本与缩小产品尺寸,现今全球包括台积电、日月光、矽品、意法、三星、尔必达、美光、格罗方德、IBM、英特尔等多家公司都已陆续投入3DIC的研发与生产。

日月光集团研发中心总经理唐和明透露,目前3DIC从设计工具、制造、封装测试等所有流程的

关键字:

台积电 3D芯片

本文研究主要考虑基于CuSn金属互化物的微凸点(μbump)作为芯片堆叠的手段。系统研究了形成金属互化物凸点连 ...

关键字:

3D芯片 堆叠 距微凸点

GTC2012大会上,曾担任斯坦福大学计算机科学系主任的NVIDIA首席科学家BillDally在接受EETimes采访时谈到了3D整合电路,技术层面上中国的崛起以及美国研发投资的现状。

关于3D芯片方面,Dally称GPU的未来存在着整合若干块3D堆叠显存的一条道路,这种设计比较有潜力发挥出更高的带宽效果,同时整体功耗更低。此前开发出HyperMemoryCube的美光实际上已经与NVIDIA商议过这一点,但Dally表示由于NVIDIA只想要自己独立设计芯片,而美光提出的要求带有在价值链上攫

关键字:

驱动之家 3D芯片

您可能听说过这样的宣传:随着目前还是平面结构的裸片向多层结构的过渡,半导体制造基础在今后几年内将发生重大转变。为了使这种多层结构具有可制造性,全球主要半导体组织作出了近10年的不懈努力,从明年开始三维(

关键字:

多维 3D芯片 设计技术

3d芯片介绍

世界上第一款3D芯片工艺已经准备获取牌照,该工艺来自于无晶圆半导体设计公司BeSang公司。BeSang公司制作的用于演示的芯片在其控制逻辑上使用了1.28亿个垂直晶体管用作内存位单元。该芯片的设计在国家Nanofab中心(韩国大田)和斯坦福Nanofab(美国加州)进行。BeSang公司称,该工艺由25个专利所保护,将允许Flash、DRAM以及SRAM放置在逻辑电路、微处理器以及片上系统上 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473