莱迪思半导体公司和Helion Technology今日宣布一系列适用于LatticeECP3 FPGA系列的压缩和加密的IP核现已上市。该系列具有有效载荷压缩系统核,提高了有限信道带宽的利用率,因此非常适合微波回程应用、宽带无线接入适用于802.16e(WiMAX)以及潜在的其他多链路多输入-多输出(MIMO)应用中的使用。在LatticeECP3器件中,IP核可以从500Mbps无缝扩展至超过3Gbps,并可用于典型的网络应用中的第2层或第3层。IP核采用了非常强大和成熟的LZRW无损压缩算法,它

关键字:

莱迪思 FPGA

莱迪思半导体公司(NASDAQ: LSCC)今天宣布,其屡获殊荣的Platform Manager™系列产品完全合格并进入量产阶段。与此量产信息发布相配合的是更新的PAC-Designer® 6.0.1设计软件,它使模拟和电路板设计师将电路板的电源管理和数字板的管理功能集成至Platform Manager器件系列。此外,现在即可获取另外11个参考设计(包括风扇控制器,边界扫描端口连接器和GPIO扩展器),这些都为使用Platform Manager产品而进行了专门的测试。

关键字:

莱迪思 电路板

莱迪思半导体公司今天宣布推出印刷版的书“Power 2 You”, 针对电路板的电源管理功能,为设计人员提供150页的技术细节和设计考虑。作者是Srirama(“Shyam”) Chandra,他是电源管理领域被认可的专家,发表了多篇有关电源管理的文章。

关键字:

莱迪思 电源管理

莱迪思半导体公司今天宣布推出其新的MachXO2™ PLD系列,为低密度PLD的设计人员提供了在单个器件中前所未有的低成本,低功耗和高系统集成。嵌入式闪存技术采用了低功耗65纳米工艺,与MachXO™ PLD系列相比,MachXO2系列提供了3倍的逻辑密度、10倍的嵌入式存储器、降低了100倍以上的静态功耗并减少了高达30%的成本。

关键字:

莱迪思 PLD

莱迪思半导体公司今日发布了ispLEVER® Classic设计工具套件1.4版。ispLEVER Classic设计软件已经升级,添加了带有HDL Analyst功能集的Synopsys Synplify Pro,以及改进的ispMACH® 4000ZE CPLD Fitter,具有更好的功耗优化功能。

Synplify Pro HDL Analyst为设计师们提供了快速直观地实现高阶寄存器传输级(RTL)Verilog或VHDL的方法。设计师可以在图和源代码之间进行交叉查询,

关键字:

莱迪思 设计工具套件 ispLEVER

引言

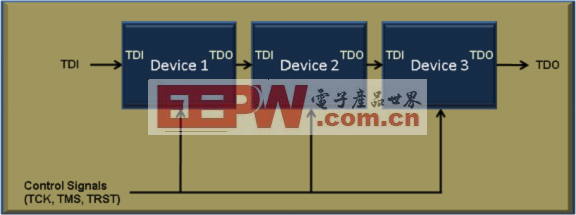

随着JTAG标准IEEE1149.1的定型,及随后开始在集成电路Intel 80486中采用,边界扫描测试已被广泛应用于测试印刷电路板的连接,以及在集成电路内进行测试。边界扫描测试受到设计人员的欢迎,因为它能够在线测试,而无需昂贵的钉床在线测试设备。然而,在大的电路板上,边界扫描链路很长,电路板设计人员面临着多种挑战,诸如故障检测和隔离、测试时间、物理布线,同时还要管理偏移,电压转换和满足各种特殊需要。传统上使用ASSP来应对这些挑战,然而基于ASSP的解决方案更为昂贵,有固定的电平和一些

关键字:

莱迪思 PLD

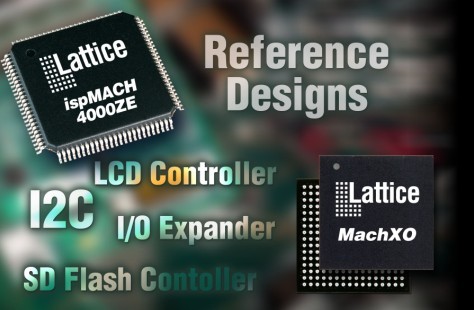

莱迪思半导体公司今天宣布已经推出了针对MachXO™和ispMACH® 4000ZE PLD而优化的超过90个参考设计。参考设计能够帮助设计人员快速和高效地进行设计,并能有效使用这些常用功能,诸如通用I/O扩展、I2C总线主/从、LCD控制器、SD闪存控制器,以及其他接口,这些功能广泛地用于各种市场,包括消费、通讯、计算机,工业和医疗等。这些参考设计与完整的文档和设计源代码结合在一起完全可以适应客户的需求,使设计人员缩短设计时间,提高工作效率并加快产品的上市。

&ldqu

关键字:

莱迪思 参考设计 PLD

莱迪思半导体公司今日宣布Nu Horizons Electronics Corp. 即日起将在全球范围内代理莱迪思的全部产品。Nu Horizons目前在整个亚太地区代理莱迪思产品。

Nu Horizons全球代理部总裁Kent Smith 表示:“Nu Horizons Electronics 非常高兴能与莱迪思一起拓展全球业务。莱迪思是全球领先的FPGA、PLD、可编程时钟和电源管理器件、软件设计工具和IP核供应商之一,并且我们的全球销售和工程师团队对于可编程逻辑技术非常了解。莱

关键字:

莱迪思 FPGA PLD 可编程时钟 电源管理器件

莱迪思半导体公司今日发布ispClock 5400D 可编程时钟器件的评估板,价格为169美元。这款新的评估板是适用于ispClock5400D差分时钟分配器件的评估和设计的易于使用的开发平台。该款评估板还可以用于查看5400D器件的性能和在系统编程,或者用作LatticeECP3™ FPGA串行协议或视频协议评估板的副板或时钟源。

通常,只有带有LVDS或LVPECL接口的价格昂贵的振荡器才可用作FPGA SERDES接口应用的参考时钟源。而现在ispClock5400D器件提供超

关键字:

莱迪思 开发平台 LatticeECP3

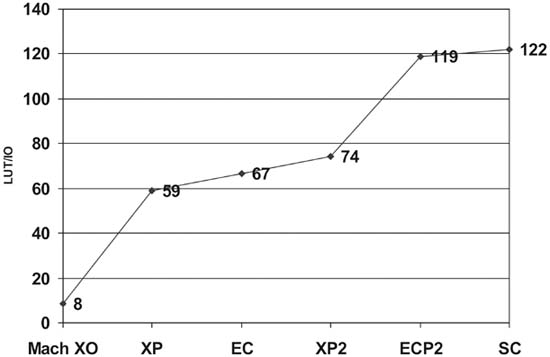

进行硬件设计的功能调试时,FPGA的再编程能力是关键的优点。CPLD和FPGA早期使用时,如果发现设计不能正常工作,工程师就使用“调试钩”的方法。先将要观察的FPGA内部信号引到引脚,然后用外部的逻辑分析仪捕获数据。然而当设计的复杂程度增加时,这个方法就不再适合了,其中有几个原因。第一是由于FPGA的功能增加了,而器件的引脚数目却缓慢地增长。因此,可用逻辑对I/O的比率减小了,参见图1。此外,设计很复杂时,通常完成设计后只有几个空余的引脚,或者根本就没有空余的引脚能用于调试。

关键字:

莱迪思 FPGA 逻辑分析仪

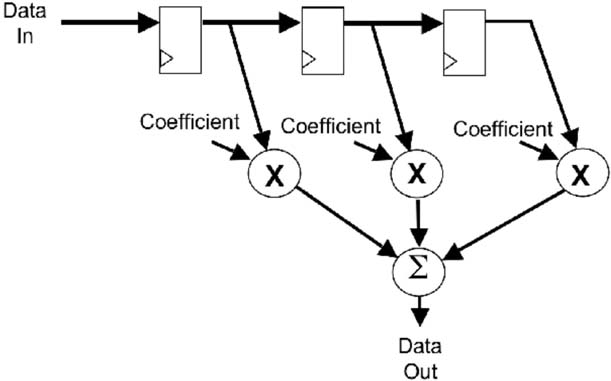

你接到要求用FPGA实现FIR滤波器的任务时,也许会想起在学校里所学的FIR基础知识,但是下一步该做什么呢?哪些参数是重要的?做这个设计的最佳方法是什么?还有这个设计应该怎样在FPGA中实现?现在有大量的低成本IP核和工具来帮助你进行设计,因为FIR是用FPGA实现的最普通的功能。

关键字:

莱迪思 FPGA FIR滤波器

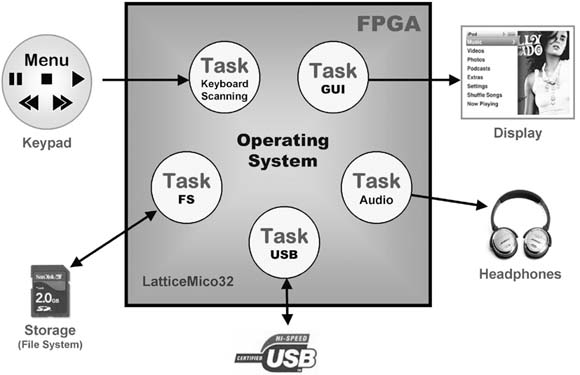

操作系统能够提高可移植性,并提供多种经过测试的抽象层,服务层和应用模块层以供选择,从而加快产品上市时间并减少应用程序出错的可能性。然而,选择一个嵌入式操作系统( OS )从来就不是一个简单的过程,因为集成嵌入式软件的方式选择余地很大,你可以完全都由自己来编写,或通过商业定制专门实时操作系统,也可以直接购买通用操作系统不作任何修改,现成的通用操作系统。FPGA性能的提高和软处理器核的出现,直接导致了可编程逻辑SoC解决方案的产生,随着这一变化,关于选择标准,设计方案以及折中考虑等传统经验也需要与时俱进以

关键字:

莱迪思 FPGA 操作系统

--第二代 EConomy Plus器件降低了50%的价格并达到双倍的密度 -- 莱迪思半导体公司近日公布了其第二代EConomy Plus 现场可编程门阵列 (FPGA)器件,LatticeECP2系列。用了富士通90纳米CMOS工艺和300毫米硅片,在大批量的情况下,此系列使得FPGA价格降到每1000查找表(LUT)低于0.50美元。与130纳米 LatticeECP FPGA相比,新的系

关键字:

LatticeECP2 莱迪思 市场

-通力合作打造出难以超越的FPGA产品系列- 莱迪思半导体公司近日宣布推出其新一代的90纳米FPGA,包含两个全新的FPGA器件系列。LatticeSC™ 系统芯片FPGA的设计宗旨是提供业界最佳的整体性能,而LatticeECP2™ FPGA则将业界成本最低的FPGA结构和高端的FPGA功能集于一身。这两个器件系列都采用了富士通公司经过优化的工艺,既满足了高容量FPGA对成本效率的要求,又能够提供拥有数百万门的系统级FPGA所需的千兆赫性能。这两个器件系列将在

关键字:

LatticeECP2 LatticeSC 富士通 莱迪思

- LatticeSC FPGA 将高速I/O、SERDES、结构化的ASIC模块 和高性能的FPGA结构集成在单个器件上 - 莱迪思半导体公司近日发布了其LatticeSCTM系统芯片FPGA系列。该系列在高速应用中有着无以伦比的性能和连通性。LatticeSC FPGA采用富士通的90纳米CMOS工艺技术并用300毫米硅片制造,能够加速芯片至芯片、芯片至存储器、高速串行

关键字:

FPGA系列 LatticeSC 莱迪思

莱迪思介绍

您好,目前还没有人创建词条莱迪思!

欢迎您创建该词条,阐述对莱迪思的理解,并与今后在此搜索莱迪思的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473