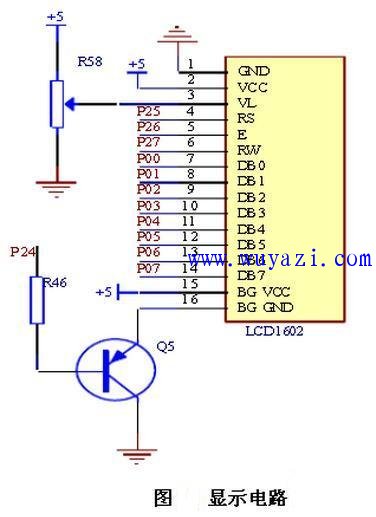

介绍了由低功耗大容量Flash闪速存储器K9K2G08及低功耗单片机MSP430F149等组成的微型低功耗大容量心电记录仪的设计,有效地解决了Holter需要大存储容量与低功耗的问题。该记录仪可完整地记录超过200小时的心电信息,具有体积小、功耗低的特点,可在需要的时候将数据传送到PC机中查看和分析心电图,特别适合于家庭监护和心电短暂异常病人的疾病诊断。

关键字:

记录仪 研制 心电 大容量 功耗 微型

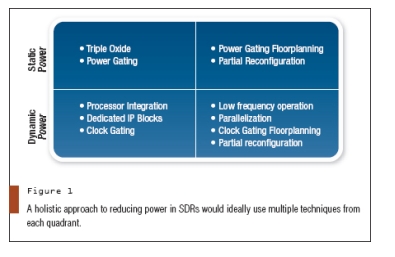

由于像美国联合战术无线电系统(JTRS)这样的计划,软件定义的无线电(SDR)早已被证实。然而,有许多问题严重地制约着SDR的广泛部署,其中相当重要的问题就是功率。

功率是在设计每一个SDR子系统时的主要考虑因素,特别是因为它们要消耗比硬件无线电更多的功率。例如,为了获得预期的无线电通信距离(依赖于链路的状况,典型值为5-10千米数量级),射频(RF)前端必须具备足够的发射功率。同样,对于靠电池工作的无线电设备,RF前端、调制解调器和加密处理子系统的功耗都直接影响无线电设备的寿命。此外,对由调制

关键字:

FPGA 无线电 SDR 功耗

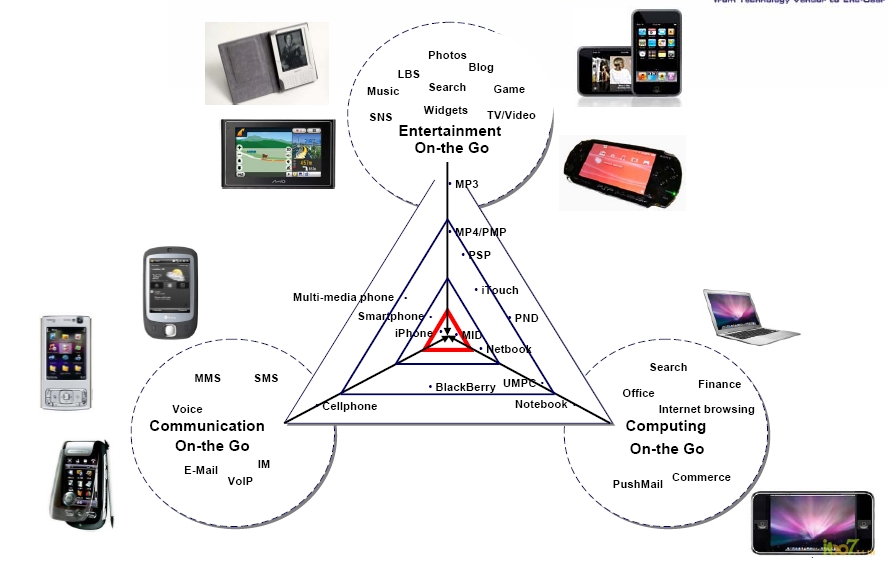

目前,便携式产品已经深入到我们生活的方方面面,成为引领半导体产业前进的主导力量,另一方面,便携式产品种类也日益繁多,MP3、MP4、PMP、UMPC、PND、MID、移动电视终端等便携式新品不断涌现,同时便携式功能日益强大,不但能提供音频、视频播放等娱乐功能,还能提供导航、上网、商务等功能,在便携式产品日新月异的同时,一个个疑问也开始困扰便携式设计工程师:未来便携式产品会融合吗?如何融合?融合哪些功能?如何应对便携式产品的电源管理挑战?2008年7月17~18日,在深圳创意时代主办的“PD

关键字:

便携式产品 Linux 3M投影 飞兆半导体 功耗 意法半导体 电源 CMMB

功耗关

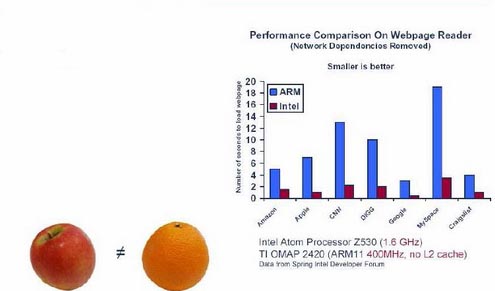

其次,功耗更低。ARM是以低功耗和近乎福利价的IP(知识产权)授权走遍天下的。Intel的功耗不低,为此推出了多核战略。不仅如此,今年三季度(9月10日左右),Intel将推出第一个针对嵌入式市场的芯片:SoC(系统芯片)处理器“Tolapai”。实现了两年前的承诺:集成了北桥和南桥。Tolapai处理器基于改良版的Pentium M核心,32-bit设计,频率600MHz、1GHz、1.2GHz,采用65nm工艺制造,集成1.48亿个晶体管,封装面积37.5×37.5mm,热设计功耗1

关键字:

Intel 嵌入式 功耗 SoC ARM

直到最近,异步电路仅仅在非常必要时才使用。由于学术界的偏见,它们通常被视为边缘产品。现在,许多商用设备已经开发了上述针对各类小众市场的功能。

关键字:

功耗 高性能 设计 核心 DSP 异步

降低便携式应用的功耗,无线手持终端设备、智能电话、PDA 以及媒体播放器等新一代便携式消费类电子产品均具有更多的特性和更高的性能,通常其尺寸也变得更小巧。由于这些最新的特性,这些设备均要求极高的功耗。

关键字:

功耗 应用 便携式 降低 德州仪器

基于ARM CPU并集成了外围功能(如实时操作系统定时器等)的μPLAT系列是一种基本系统级LSI开发平台。高速及低功耗的μPLAT-92平台专为W-CDMA、PDA及其它便携式终端(如互联网设备)应用而开发。μPLAT-92是以硬IP为特征的硬件开发与集成环境的平台总称:μPLAT-92内核包括一颗ARM920T CPU及运行操作系统所需的最少外围I/O器件;电源管理IP及原型板也包括在内。这不仅能提高系统级LSI的运行速度及降低其功耗,而且还能缩短规模不断提高的大型系统级LSI的开发时间,并使用户能专

关键字:

功耗 微型 平台 高速 开发 系统 LSI 面向

由于目前大部分能源是从化石燃料取得,过度地消耗石油等能源,引发了环境问题、经济问题和政治问题等,使我们的世界不那么美好了。

半导体如何帮助解决能耗?

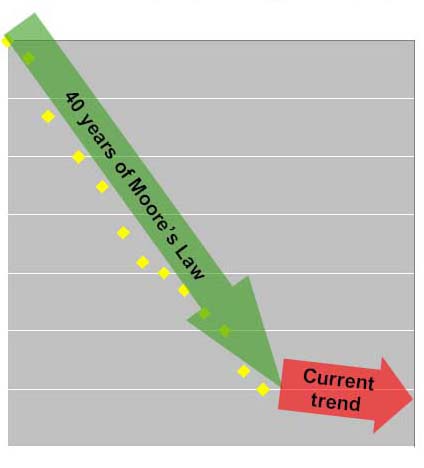

过去20年,功耗一直在上升,而不是下降。摩尔定律出什么错了?因为功耗!每个晶体管的单位功耗下降了,这毫无疑问。但是每个芯片的晶体管数量增长更快,因此导致芯片的总功耗增加。一年前,Intel发明了45nm的工艺-以Hf(铪)为基础的High-k(高k)材料作为绝缘层材料,代替了传统的二氧化硅,大幅减少漏电量。但是没有完全解决问题,因为在电路中功

关键字:

功耗 半导体 能耗 新能源 200806

目前,处理器性能的主要衡量指标是时钟频率。绝大多数的集成电路 (IC) 设计都基于同步架构,而同步架构都采用全球一致的时钟。这种架构非常普及,许多人认为它也是数字电路设计的唯一途径。然而,有一种截然不同的设计技术即将走上前台:异步设计。

关键字:

功耗 高性能 设计 核心 DSP 异步

这一新技术的主要推动力来自硅技术的发展状况。随着硅产品的结构缩小到 90 纳米以内,降低功耗就已成为首要事务。异步设计具有功耗低、电路更可靠等优点,被看作是满足这一需要的途径。

关键字:

功耗 高性能 设计 核心 DSP 异步

ABI Research的最新研究报告指出,RFID读取器正在向高度集成化和创新性发展。

读取器电路中的低频 (LF) 和高频 (HF) RFID电路由于能够与体积更小功耗更低的器件集成,正在成为市场的领先器件。类似的集成化趋向在超高频 (UHF) RFID 读取器电路也在进展中,集成有第一代UHF读取器电路的产品正在走向市场。

ABI Research的主任分析师Pete Poorman说:“EPCglobal Gen 2 无源UHF RFID 标准实践证明性能可靠,

关键字:

RFID ABI 功耗 集成化

许多嵌入式ARM处理器的系统都是基于电池供电的能量供应方式,而处理器的功耗对于整个SoC芯片至关重要,因此ARM处理器的低功耗优势可以充分节省能量消耗。总之,当前的典型功耗的电流图并不依赖于标准过程、标准集或工作负载。

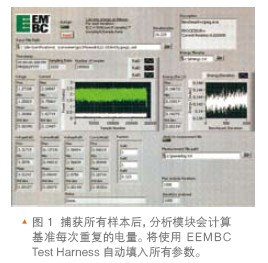

EnergyBench提供若干工具,这些工具可容易低与经济实用的硬件结合使用,以便使用E EM B C开发的标准方法测量典型功耗。不过,除了处理器之外,具体芯片设计和集成到芯片内部的外围模块也是影响芯片功耗的重要因素。虽然许多芯片供应商都会在产品的datasheet中提供

关键字:

ARM SoC 功耗 EnergyBench

尽管手机设计人员不断地将语音、相机、GPS及其他功能集成在一个不超过半英寸厚的外壳中,便携式媒体播放器设计者将微控制器、硬驱和音频电路等整合在口袋大小的封装中,但是便携式设计集成多种功能的压力仍然巨大。

关键字:

设计 功耗 挑战 便携式 应对 电源 管理 IC 利用

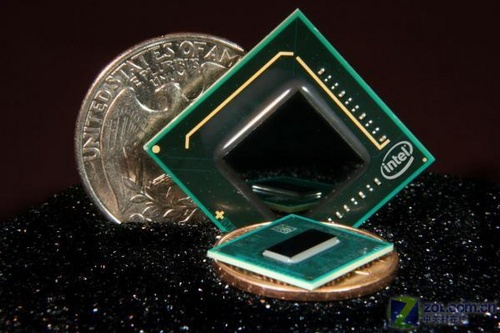

说道Atom处理器它可以算是英特尔有史以来最小的产品之一,当然这种小不仅仅只是对它内含有4700万个晶体管以及25平方毫米的面积来诠释。而Atom的功耗也足以令其对手汗颜,产品的热设计功耗为0.6瓦到2.5瓦之间,但是处理器的频率却能达到1.8GHz,相比目前的主流酷睿2双核处理器的热设计功耗也要25至35瓦。

根据英特尔对Atom处理器的定位,该产品将会应用于智能手机、UMPC等超便携移动设备,这也说明了该产品的应用范围被限定在了那些对性能要求较低的层

关键字:

Atom 功耗 英特尔 Computex 联想

根据摩尔定律,每18个月(起初是24个月)芯片上的晶体管密度就会翻番,但是前几年功耗问题曾一度困扰Intel等公司的发展。为此,Intel对摩尔定律进行了大胆的修正,指出摩尔定律是晶体管密度、性能和功耗的折中发展规律。为此,多核开创了一个崭新的计算时代。

图1 原摩尔定律不再有助于功耗降低

通常认为,多核设计与优化的处理器相互协同作用,才能带来芯片能耗降低的地震(图2)。多年来一直倡导在SoC中进行多核设计,在可配置多核方面独树一帜的Tensilica,在多核低功耗方面取得了巨大的突破,产

关键字:

摩尔定律 芯片 晶体管 功耗 处理器

功耗介绍

定义

功率的损耗,指设备、器件等输入功率和输出功率的差额。功率的损耗。电路中通常指元、器件上耗散的热能。有时也指整机或设备所需的电源功率。

功耗同样是所有的电器设备都有的一个指标,指的是在单位时间中所消耗的能源的数量,单位为W。不过复印机和电灯不同,是不会始终在工作的,在不工作时则处于待机状态,同样也会消耗一定的能量(除非切断电源才会不消耗能量)。因此复印机的功耗一般会有两个,一个是 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473