基于赛灵思FPGA的数字频域干扰抵消器

系统方案

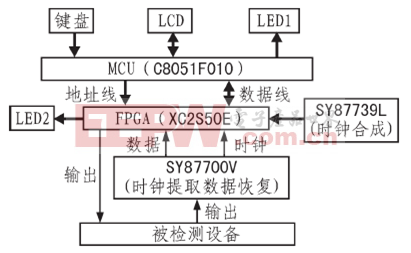

本文引用地址:https://www.eepw.com.cn/article/99723.htm完整的系统从数字下变频后的基带数据开始,至数字上变频的前端为止,包括系统同步和干扰抵消两大组成模块,系统框图如图2所示,其简要介绍如下:

(1)在没有干扰的情况下,所采集的数据源从A点输入,然后将其构造为WCDMA信源,作为频域干扰抵消模块的输入。为了使干扰抵消模块正确运转,在本设计中的B点输出信号为每个码片4采样。

(2)为体现频域干扰抵消的作用,在系统中必须模拟一个干扰信号。本设计将D点的输出经过功放(PA)作为干扰信号。

(3)将干扰信号经过多径信道,反馈到B点与WCDMA信号叠加,再进入干扰抵消模块。为了抵消干扰,将E点的输出反馈到干扰抵消模块作为参考信号。在下文中,将此反馈支路称为辅链路;而干扰抵消+功放的链路称为主链路。

(4)有干扰的信号经过频域干扰抵消模块,输出抵消后的无干扰信号给同步模块,即D点。同步模块进行三步搜索,得到帧头以及扰码信息。对同步后的码片信号进行解扰解扩后得到信息数据,如图中G点输出。

(5)在开关1处,可以选择:有干扰的信号(C点)或者干扰抵消后的信号(D点)输入同步模块,并输出显示。

(6)在开关2处,可以选择:数据源直接显示(A点),或者是同步后解出的数据显示(G点)。

WCDMA文章专题:WCDMA是什么意思

评论