LEON2应用于数字机顶盒CPU的FPGA仿真

Gaisler Research公司还提供了比较完善的基于LEON2的GNU软件开发环境。使用者可以使用TSIM或GRMON进行LEON内核的调试仿真。 LECCS是专门针对LEON的交叉编译系统,可以进行C/C++的编译和调试。SnapGear Linux是基于LClinux的实时Linux内核,它的LEON版提供了对LEON处理器的全面支持,可以支持MMU和NOM—MU等不同配置方案。

本文引用地址:https://www.eepw.com.cn/article/273880.htm由以上描述可以看出,LEON2具有强大的硬件配置和完备的软件开发环境支持,可以承担数字机顶盒CPU要求的各种信号处理任务。

3.1 硬件平台的建立

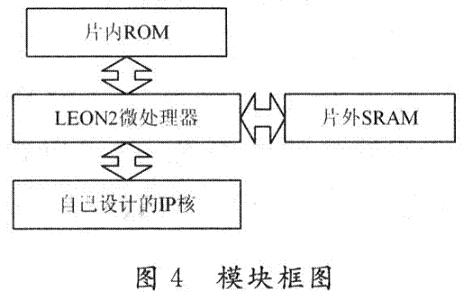

图4就是基于LEON2的平台的模块框图。LE—ON2处理器作为核心部分,片内ROM存放Monitor负责系统初始化和将程序拷贝到片外SRAM内的任务,片外RAM是FPGA开发板上Memory,用来存放程序和数据。设计的IP核通过AHB总线和LEON2相互交互。

FPGA开发板主要有以下资源:50 MHz有源时钟;1块Altera公司的核心FPGA芯片EP2C20F484一C8,逻辑单元18 752个;2片512 KB的IS61LV25616一AL SRAM芯片组成32 b宽共1 MB容量,其中每片设计为可兼容1 MB,总共最大可扩充到2 MB;JTAG接口(通过JTAG接口可以从PC机上对EP2C20F484C8进行编程);串口与计算机COMl相连,可以用于程序下载。

将配置好的LEON2的VHDL代码,加入设计的HDL代码,一起使用Synplify综合工具生成FPGA的网表文件;然后使用Quartus进行布局布线,将LEON2核同片内ROM和片外SRAM连接,布局布线完成后生成相应的SOF文件;通过JTAG端口将SOF文件下载到片子上去,对FPGA硬件进行配置,最后占用FPGA资源是5 800个逻辑单元,可以达到的时钟频率最大为46 MHz。

3.2 软件设计

由于Quartus软件可以预先配置EP2C20F484C8片上ROM,所以可以在LEON2的片上ROM预先配置好的1 KB大小的Monitor软件。Monitor的主要作用是在LEON2系统reset初始化时首先对处理器初始化,对LEON2的存储配置寄存器进行配置;然后向UART口发送启动信息;等待UART信息。当软件部分使用交叉编译器LECCS在PC上编译完毕后,PC机通过UART口和FPGA开发板相互通信,就可以将编译好的srec文件下载到:FPGA开发板上,放置在片内ROM里面的Monitor程序就读入程序的内容以及程序的起始地址。开始Monitor将srec程序拷贝到SRAM程序区,等全部程序下载好以后,Monitor最后1条程序就会自动跳转到程序的起始位置,执行SRAM里的程序。这样就可以反复修改程序,反复下载程序,便于软件的开发和调试。

4 结 语

通过将片上系统映射到FPGA,这样可以在接近运行速度的前提下,验证硬件和软件。这样不仅为软件部分能尽早地进行开发与调试工作提供了原型,同时也可以在实际运行中发现一些在系统设计中没有注意的地方。最终可以缩短设计周期,同时为ASIC设计一次成功提供了更大的把握。

在FPGA开发板上建立基于LEON2处理器的SoC平台后,使用这个原型系统,就可以很容易验证系统的性能,并且加速软件开发调试流程。

fpga相关文章:fpga是什么

数字滤波器相关文章:数字滤波器原理

评论