完美的时序:用抖动与相位噪声测量做时钟分频

表1,时域仪器-频域仪器之间的差异

对大部分器件来说,两个时钟信号有相同JO的直觉是正确的,虽然事实上,一个被2除的时钟信号的相位噪声要比原时钟信号的相位噪声低6dB。注意对于除以2的情况,6dB=20×log2。

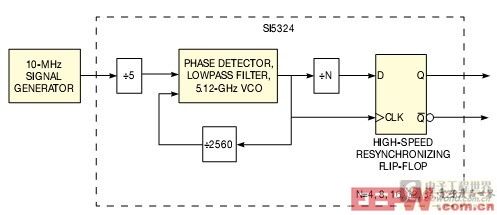

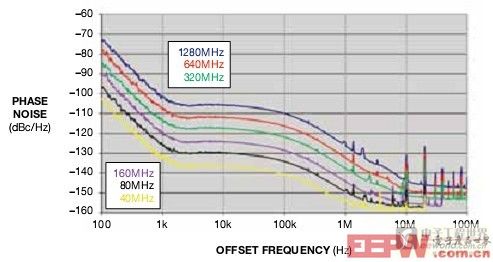

下面的例子给出了相位噪声与抖动被2除的效果。这些测量采用了一只Silicon Laboratories的Si5324 PLL器件(图5)。注意,高速VCO对输出时钟做再同步,而不管最终的输出频率,这意味着对所有可能的分频器值,边沿的形状与位置都应是相同的。唯一不同的应该是在给定时间间隔内出现的少数几个时钟边沿。虽然存在一些重新定时噪声,但它对所有分频器值都是一样的(图6)。

图5,测量采用了Silicon Laboratories的Si5324 PLL器件。

图6,高速VCO重新同步输出时钟,而与最终输出频率无关,这意味着对所有可能的分频值,边沿形状与位置都应相同。唯一的区别应是在给定的时间间隔内,出现较少的时钟边沿。

图中的六根曲线基本相同,但垂直方向相差6dBc/Hz。对所有偏移频率与分频器值,这6dB的间隔都相对恒定,只有一个或两个例外。在图的右侧,时钟(或载波)的偏移为最大,曲线之间的相对垂直偏移被压缩。当时钟频率降低时,压缩也增加。当时钟频率和相位噪声曲线值减小时,这个压缩也变得更明显。出现压缩的原因是,Agilent技术公司E5052B型信号源分析仪的本底噪声接近于Si5324 IC的相位噪声或抖动产生值。因为Si5324的超低抖动与低载波频率相结合的效应,才使本底噪声成为一个问题。表2给出了六张图各自的抖动值,抖动从100Hz~20MHz做积分,所有抖动值均为飞秒rms。

注意当输出频率降低时,抖动会略微增加,这证明了,输出抖动是一个相对恒定的值,尽管相位噪声曲线之间有6 dB的分离度。在最低输出频率上,抖动增加的速率变得更明显。下面让我们看看两种rms相位噪声值的增长来源:仪器本底噪声与混叠。

本底噪声,相位噪声

在低时钟频率下,仪器的本底噪声可能成为极低抖动时钟相位噪声测量的限制性因素。某种程度上,你测量的是自己的设备,而不是DUT。即使当时钟频率降低时,相位噪声曲线单调地减小,rms沿抖动也几乎保持恒定不变,因为相位噪声积分是用时钟周期来改变rms抖动值的大小。

为演示这种情况,考虑对相位噪声积分,产生一个rms抖动值的过程。大多数现代相位噪声设备都会产生一个有两栏的文件,通常是一个CSV(逗号分隔值)文件。其中一栏列出了与时钟(或载波)频率偏差的频率值,单位为赫兹。另一栏则列出了在偏移频率处,参照每赫兹载波的相位噪声值(分贝)。因此,这些栏中包含的各对数据点描述了对时钟频率一个确定偏移处的相位噪声。用方程:线性值=10(dBc/Hz)/10将参照每赫兹载波的分贝值转换为线性值后,对所有频率偏移点的曲线下面积求和做积分。

分频器相关文章:分频器原理

评论