一种基于SOPC技术的内存映射型LCD控制器设计

2.2 寄存器模块(register_bank)

本文引用地址:https://www.eepw.com.cn/article/248875.htm该模块为Avalon总线从端口设备,可以通过NiosⅡ Processor设置和读取显存起始地址、显示大小、显示颜色位数及相关控制参数。

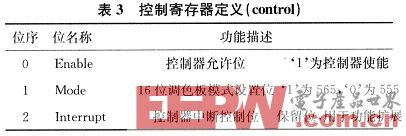

寄存器模块中共定义了4个寄存器;显存起始地址寄存器、显示参数寄存器、控制寄存器和状态寄存器。各寄存器的读写控制、定义及功能描述如表2所示。

其中,显示参数寄存器(size)中“色数”标志位,值为1表示8位颜色显示,值为0表示16位颜色显示。状态寄存器(status)大小为两位,可与控制寄存器中的中断位(Interrupt)配合使用,为保留位。控制器寄存器的定义如表3所示。

2.3 数据缓存模块(line_buffer)

该模块设计采用了双口RAM,由MegaWizard Plug-In Manager生成,其存储空间约为一行数据所占的空间,用于暂存显示数据。由于DMA不是直接将显存中的数据传给时序发生器,而在中间使用了双口RAM 做数据缓存,这样DMA和时序发生器的读、写时序不必严格对应,简化了结构设计。同时,用于16位彩色显示时,可通过数据缓存模块将总线32位的数据输入变为16位的数据输出给时序发生器;而在8位彩色显示时,可通过数据缓存模块将32位输入变为8位输出,实现了数据位数的转化,方便的时序发生器内部的数据操作。

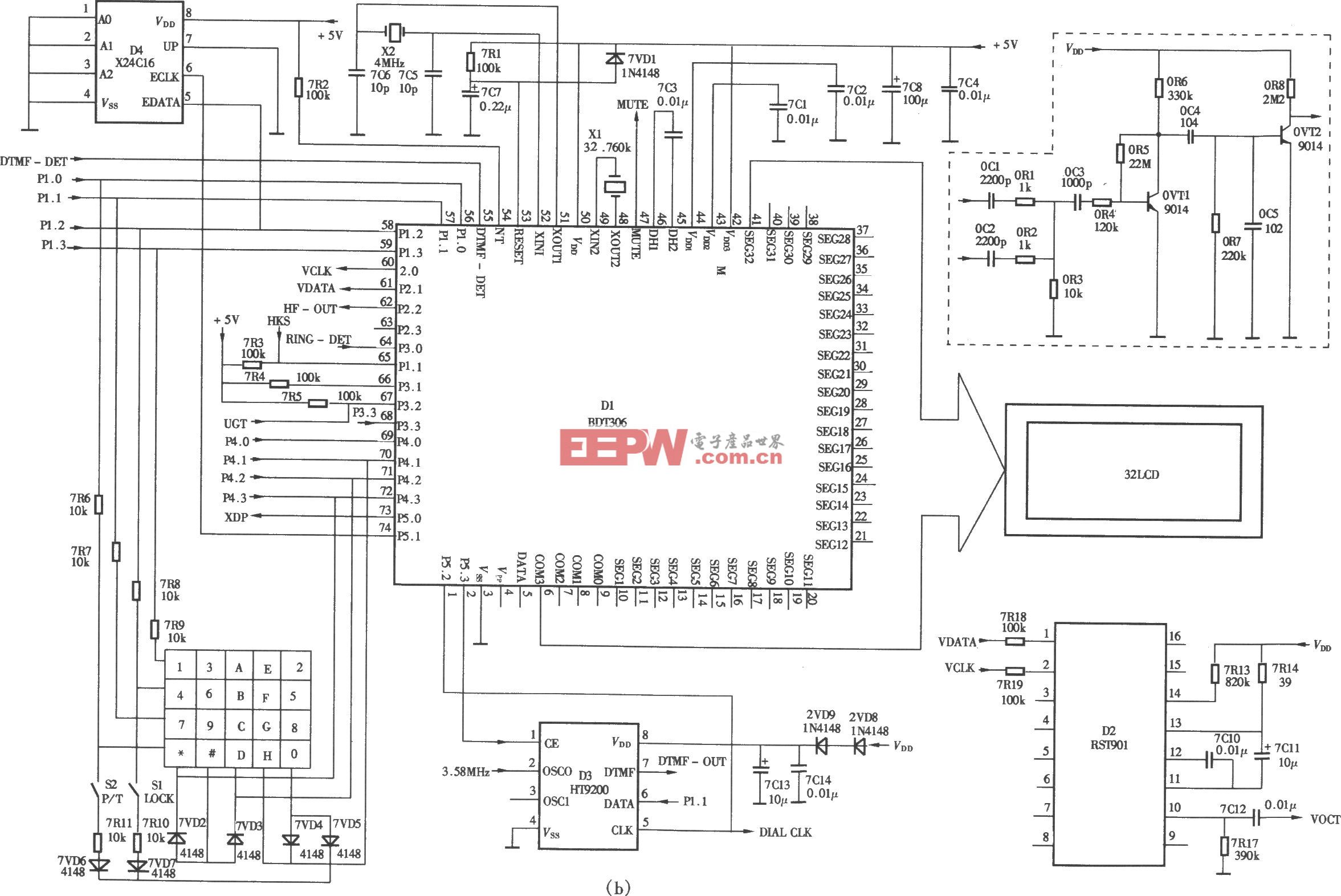

2.4 DMA模块(image_dma)

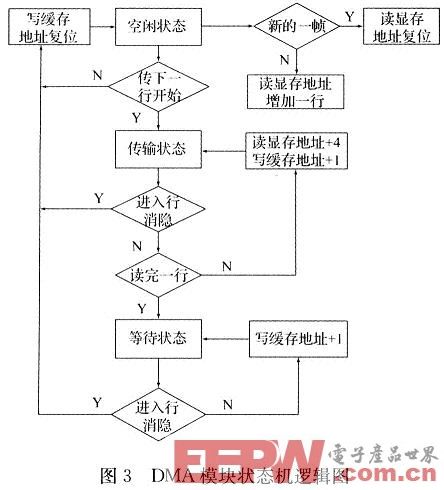

该模块为Avalon总线主端口设备,它负责向Avalon总线提供有效的地址、数据和写请求信号,并在时钟上升沿发起总线传输,读取显存中的数据;同时,DMA模块产生写数据缓存的地址和数据,将显示数据正确地从显存传送到数据缓存。DMA模块为三状态的状态机,包括空闲状态、传输状态、等待状态,各状态机逻辑关系如图3所示。

2.5 时序发生器(LCD_driver)

时序发生器模块主要有4个主要功能:

(1)产生驱动LCD的行扫描信号(hsync)、列扫描信号(vsync)、数据使能信号(blank_n);

(2)产生读双口R_AM缓存的地址信号;

(3)产生行、场消隐信号,控制DMA模块启动、停止数据传输;

(4)将显示数据RGB按正确的时序、指定模式输出。

常用的16位彩色显示可分为555、565(即RGB信号分量所占位数)两种显示模式,控制器通过判断控制寄存器中的模式设置位将RGB信号以不同的格式输出。

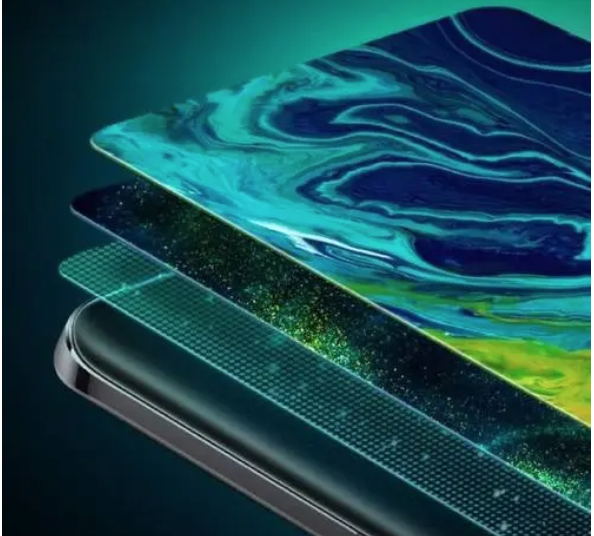

2.6 实验平台的设计及内存映射型LCD控制器的验证

为验证该控制器,本文设计了以CycloneⅡ系列EP2C8Q208C8为主芯片的SOPC评估电路板。实验平台的TFT-LCD选用 SAMSUNG公司的LTA104S1-L01,该LCD大小为10.4英寸、分辨率为800×600,可实现16位真彩色显示。由于LTA104S1- L01接口为LVDS,本文设计了以DS90CF363为主芯片外接的接口板,以实现RGB到LVDS信号的转换实验结果说明,本控制器能有效地解决显存读写问题,设计完全符合预期要求。实验平台及显示效果如图4所示。

3 结束语

本文设计的内存映射型LCD控制器,能有效地解决显存读写冲突。同时与文献[8]中的控制器相比,由于使用自定义的DMA代替了原有的DMA IP Core,数据的传输不必由CPU产生中断发起,而完全由控制器发起,从而减轻CPU的运行负担。同时,该设计还具有占用逻辑单元少、适用范围广、灵活性强、实用性强、扩展性强等特点,可用于多种分辨率LCD的显示控制,具有一定的实用价值。

LCD显示屏相关文章:lcd显示屏原理

lcd相关文章:lcd原理

评论