基于AD9852的雷达回波模拟器设计

摘要 基于直接数字频率合成技术DDS的原理,分析了影响DDS频率输出的核心因素。在此基础上仿真验证了相位累加器的位数对DDS频率输出的作用。介绍了一种DDS芯片AD9852并基于这种芯片提出了一种雷达回波模拟器的设计,并分析了DDS芯片的优缺点。该设计能够稳定地产生70 MHz载频的雷达回波,较好地模拟出所需回波。

本文引用地址:https://www.eepw.com.cn/article/246641.htm关键词 DDS;相位累加器;AD9852

直接数字频率合成技术(DDS)是继直接频率合成技术和锁相环式频率合成技术之后的第三代频率合成技术,它的原理是在采样频率一定的条件下,通过控制两次连续采样之间的相位增量来改变所得的离散序列频率,然后经保持和滤波,唯一回复出该频率的模拟信号。与其他频率合成方法相比,直接数字频率合成器具有频率街边速度快、频率分辨率高、输出相位连续、可编程和全数字化、便于集成等优点。本文在分析了DDS的基本原理的基础上,提出了一种基于DDS芯片AD9852的雷达回波模拟器的设计。

1 DDS原理

1.1 DDS的基本原理

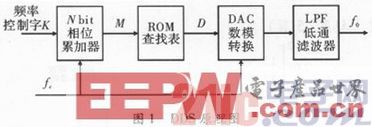

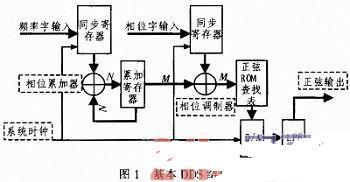

DDS的工作原理是基于相位与幅度的对应关系,通过改变频率控制字K来改变相位累加器(位数为N)的相位累加速度,然后在固定时钟的控制下取样,取样得到的相位值(取相位累加器的高M位)通过相位幅度(ROM查询表法,即在ROM中存放不同相位对应的幅度序列,然后相位累加器的输出对其寻址)。转换得到相位值对应的幅度序列,幅度序列通过数模转换及低通滤波得到余弦波输出。DDS原理如图1所示。

DDS的核心是相位累加器,它由一个N位相位加法器和一个N位相位寄存器组成。每生成一个时钟脉冲(频率为fc),加法器将频率控制字K与寄存器输出的数组相加,把相加的结果送到寄存器的数据输出端。寄存器将加法器在上一个时钟脉冲作用后产生的相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟脉冲的作用下,不断对频率控制字进行线性相位累加,当相位累加器产生一次溢出时,则完成了一次周期性操作,这就是DDS合成信号的周期,溢出频率是DDS的输出频率f0。输出频率f0与时钟频率fc、频率控制字K以及相位累加器位数的公式为

通过改变频率控制字K,就可改变输出频率的值。由奈奎斯特采样定理可知,DDS的最大输出频率为

fmax=fc/2 (2)

输出信号频率的分辨率即最低的合成频率为

1.2 DDS的功能仿真

通过DDS的原理可知,实际运用中,输出频率f0、时钟频率fc以及相位累加器位数N均已知,则频率控制字K为

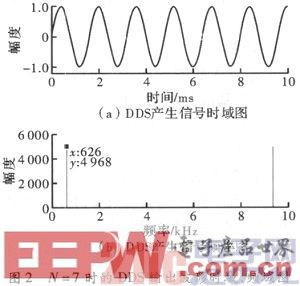

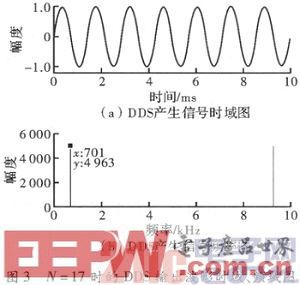

通过Matlab对DDS进行功能仿真,在相同的输出频率f0和时钟频率fc下,改变相位累加器的位数N,则频率控制字K也改变,比较最后经过DDS仿真的输出频率f0。分别设置输出频率为700 Hz,时钟频率为10 kHz,相位累加器的位数分别设置为N=7和N=17,最后实际的输出频率如图2和图3所示。

由图2和图3比较可知,因相位累加器位数的不同,频率控制字K也不同,DDS输出的频率就不同。相位累加器的位数N=7时,实际输出的频率只有626 Hz,距离预期输出频率700 Hz相差较大;而当N=17时,实际输出的频率为701 Hz,接近理想的输出频率700 Hz。因此可知,在相同的采样频率和预期的输出频率下,相位累加器的位数N决定了实际的输出频率。即相位累加器位数N越大,实际输出频率越接近预期输出频率。

2 AD9852芯片

AD9852数字合成器是一种高集成设备,它采用先进的DDS技术,配上高速、高性能的D/A转换器来实现数字化可编程的合成器功能。当接入精确时钟源时,AD9852能产生一种高稳定度的,频率-相位-幅度-可编程的余弦波,这种波可用于通信、雷达中作为灵活的本振信号以及其他多种用途。AD9852的改进型-高速DDS芯片可提供48位频率分辨率。截断到17位的相位确保能产生优质的SFDR.AD9852电路结构,允许输出信号的频率达150 MHz,这使其数字上能以每秒100 MHz的速率调谐成新的频率。

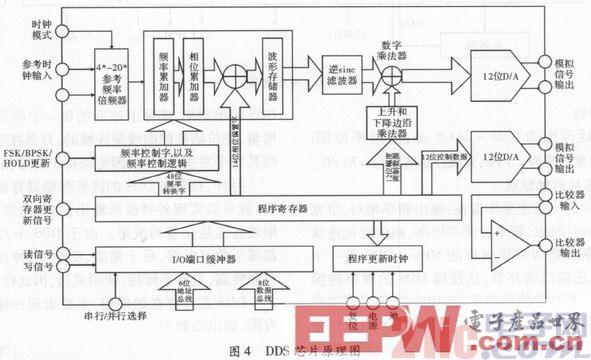

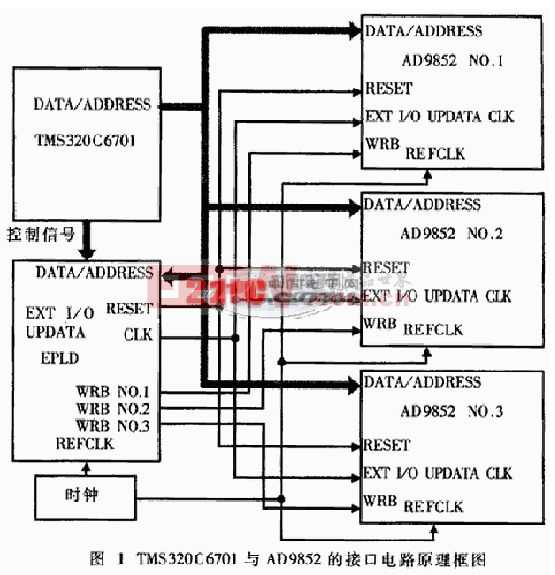

如图4所示,AD9852内部包括一个具有48位相位累加器、一个可编程时钟倍频器、一个反sinc滤波器、两个12位300 MHz DAC,一个高速模拟比较器以及接口逻辑电路。其主要性能特点如下:(1)300 MHz的系统时钟。(2)能输出一般调制信号,FSK,BPSK,PSK,CHIRP和AM等。(3)100 MHz时具有80 dB的信噪比。(4)内部有4~20倍的可编程时钟倍频器。(5)两个48位频率控制字寄存器,能够实现较高的频率分辨率。(6)两个14位相位偏置寄存器,提供初始相位设置。(7)带有100 MHz的8位并行数据传输口或10 MHz的串行数据传输口。

AD9852有40个程序寄存器,对AD9852的控制就是对这些程序寄存器写数据实现的。通过并行总线将数据写入程序寄存器时,实际只是暂存在I/O缓冲区中,只有提供更新信号,这些数据才会更新到程序寄存器。AD9852提供内部更新和外部更新两种更新方式。内部更新通过更新时钟计数器完成,当计数器计自减为零后会产生一个内部更新信号;外部更新需要在外部更新管脚上给予一个高电平脉冲。默认的更新模式为内部更新,可以通过设置控制寄存器0x1F的0位进行修改。

模拟信号相关文章:什么是模拟信号

尘埃粒子计数器相关文章:尘埃粒子计数器原理 锁相环相关文章:锁相环原理

评论