FlexRay的通信控制器媒体接入控制设计

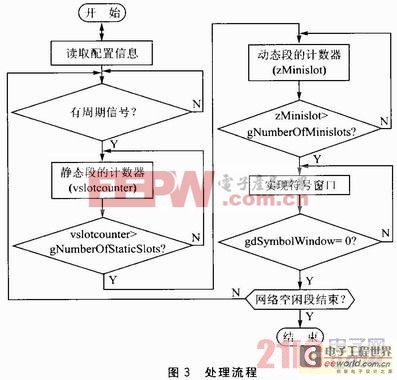

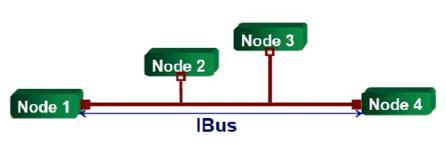

具体处理流程如图3所示。

2 设计验证

确保设计正确性的关键是设计验证,主要通过逻辑功能仿真。逻辑功能仿真是在不考虑信号延迟的情况下对设计的逻辑功能进行验证。验证过程是:首先编写好设计的HDL代码;然后编写对应的TestBcnch,对设计进行关键性的验证;最后利用仿真软件ModelSim进行模拟,查看波形或者输出,若发现错误则查找错误原因、修改代码或者测试文件,直到符合设计要求。

设计验证的首要工作是根据FlexRay协议设定具体的参数。具体参数的设定如下:gMacroPcrCycle=48,gdStaticSlot=4,pMicroPerCyc le=672,gNumberOfMinislots=15,gdSymbolWindow=3,gdActionPointOffsct=1,gdMinislotActionPointOffset=1。

图4是时钟产生模块的周期信号图。从图中可以看到,时钟产生模块需要等待晶振的最小时钟节拍信号,然后进行判断产生周期信号。当周期信号开始时,周期编号从默认的63变为0,然后一直编号下去直到63。

图5是对图4产生的周期信号开始周期的四个段的划分。从图中可以看到,0周期分为静态段、动态段、符号窗口、网络空闲段。

图6是静态段的媒体接入方式。从图中可以看到,槽计数器(vslotcounter)从1开始编号直到用户配置的值。在第一个静态槽实现了媒体接入。

图7是动态段的媒体接入方式。从图中可以看到,周期8的动态段有动态槽计数器zMinislot,从0开始编号直到用户配置的值。在第5个动态槽实现了媒体接入。

结语

本文介绍了基于FlexRay协议的媒体接入控制的设计过程,并进行了设计验证。从仿真结果分析,它符合协议的要求,能够生成通信控制器的时钟周期,将时钟周期进一步划分为4个段,并且给出静态段和动态段的具体媒体接入方式。

评论