MOSEFT分析:理解功率MOSFET的开关损耗

开通过程中产生开关损耗为

![]()

开通过程中,Crss和米勒平台时间t3成正比,计算可以得出米勒平台所占开通损耗比例为84%,因此米勒电容Crss及所对应的Qgd在MOSFET的开关损耗中起主导作用。Ciss=Crss+Cgs,Ciss所对应电荷为Qg。对于两个不同的MOSFET,两个不同的开关管,即使A管的Qg和Ciss小于B管的,但如果A管的Crss比B管的大得多时,A管的开关损耗就有可能大于B管。因此在实际选取MOSFET时,需要优先考虑米勒电容Crss的值。

减小驱动电阻可以同时降低t3和t2,从而降低开关损耗,但是过高的开关速度会引起EMI的问题。提高栅驱动电压也可以降低t3时间。降低米勒电压,也就是降低阈值开启电压,提高跨导,也可以降低t3时间从而降低开关损耗。但过低的阈值开启会使MOSFET容易受到干扰误导通,增大跨导将增加工艺复杂程度和成本。

2 关断过程中MOSFET开关损耗

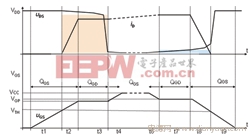

关断的过程如图1所示,分析和上面的过程相同,需注意的就是此时要用PWM驱动器内部的下拉电阻0.5Ω和Rg串联计算,同时电流要用最大电流即峰值电流6.727A来计算关断的米勒平台电压及相关的时间值:VGP=2+6.727/19=2.354V。

关断过程中产生开关损耗为:

![]()

Crss一定时,Ciss越大,除了对开关损耗有一定的影响,还会影响开通和关断的延时时间,开通延时为图1中的t1和t2,图2中的t8和t9。

图2 断续模式工作波形

Coss产生开关损耗与对开关过程的影响

1 Coss产生的开关损耗

通常,在MOSFET关断的过程中,Coss充电,能量将储存在其中。Coss同时也影响MOSFET关断过程中的电压的上升率dVDS/dt,Coss越大,dVDS/dt就越小,这样引起的EMI就越小。反之,Coss越小,dVDS/dt就越大,就越容易产生EMI的问题。

但是,在硬开关的过程中,Coss又不能太大,因为Coss储存的能量将在MOSFET开通的过程中,放电释放能量,将产生更多的功耗降低系统的整体效率,同时在开通过程中,产生大的电流尖峰。

开通过程中大的电流尖峰产生大的电流应力,瞬态过程中有可能损坏MOSFET,同时还会产生电流干扰,带来EMI的问题;另外,大的开通电流尖峰也会给峰值电流模式的PWM控制器带来电流检测的问题,需要更大的前沿消隐时间,防止电流误检测,从而降低了系统能够工作的最小占空比值。

Coss产生的损耗为:

![]()

对于BUCK变换器,工作在连续模式时,开通时MOSFET的电压为输入电源电压。当工作在断续模式时,由于输出电感以输出电压为中心振荡,Coss电压值为开通瞬态时MOSFET的两端电压值,如图2所示。

2 Coss对开关过程的影响

图1中VDS的电压波形是基于理想状态下,用工程简化方式来分析的。由于Coss存在,实际的开关过程中的电压和电流波形与图1波形会有一些差异,如图3所示。下面以关断过程为例说明。基于理想状态下,以工程简化方式,认为VDS在t7时间段内线性地从最小值上升到输入电压,电流在t8时间段内线性地从最大值下降到0。

图3 MOSFET开关过程中实际波形

评论