时域反射仪的硬件设计与实现----关键电路设计(一)

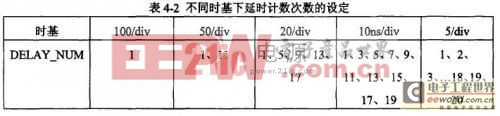

在表4-1中已经介绍过,在不同时基情况下,延时时间△t各不相同,最小延时间隔为0.2ns(5ns/div),最大延时间隔为2ns(50ns/div),因此随着时基的变化,延时间隔和采样次数都相应会不同。表4-2给出了在不同时基下延时间隔的设定。

3.1.3脉冲信号放大和分离

3.1.3.1脉冲信号放大

从FPGA的I/O口送出的脉冲信号,如果直接送到被测电缆上,测量效果必定会很差,首先因为FPGA的I/O引脚输出电流不大,导致驱动能力(带载)不足,同时由于FPGA的供电电压为+3.3V,则使I/O口的输出脉冲幅度最大只有+3.3V,如此小的电压幅度以及低的带载能力,被送到电缆后,由于电缆损耗的原因,观测到的反射脉冲幅度可能会很小,影响测量准确度。为了改善以上不足之处,就必须对脉冲信号进行放大处理,以增强脉冲信号的带负载能力,同时提高脉冲信号输出幅度。

对脉冲信号的放大必须要保证脉冲信号的完整性,不能将脉冲信号放大后,输出的脉冲信号与输入信号相比发生了较大的失真,比如上升沿特性变差等。为此本设计选用了TI公司宽带高速运放OPA691,该运放具有以下优良特性:

灵活的电源供电范围:﹢5V~+12V(单电源)、±2.5V~±6V(双电源)。

单位增益下的带宽(Bandwidth)为:280MHz(G=l)

高输出电流:190mA

输出电压范围:±4.0V

高压摆率(slew rate):2100V/us

低电源电流:5.lmA

关断模式下电流:150uA

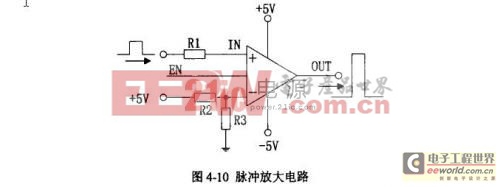

利用OPA691设计的脉冲信号放大电路如图4一10所示。

评论