时域反射仪的硬件设计与实现----关键电路设计(一)

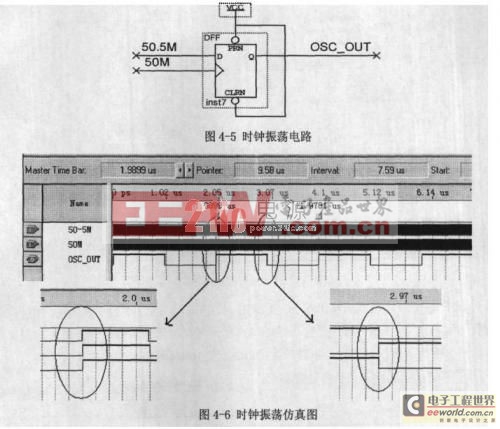

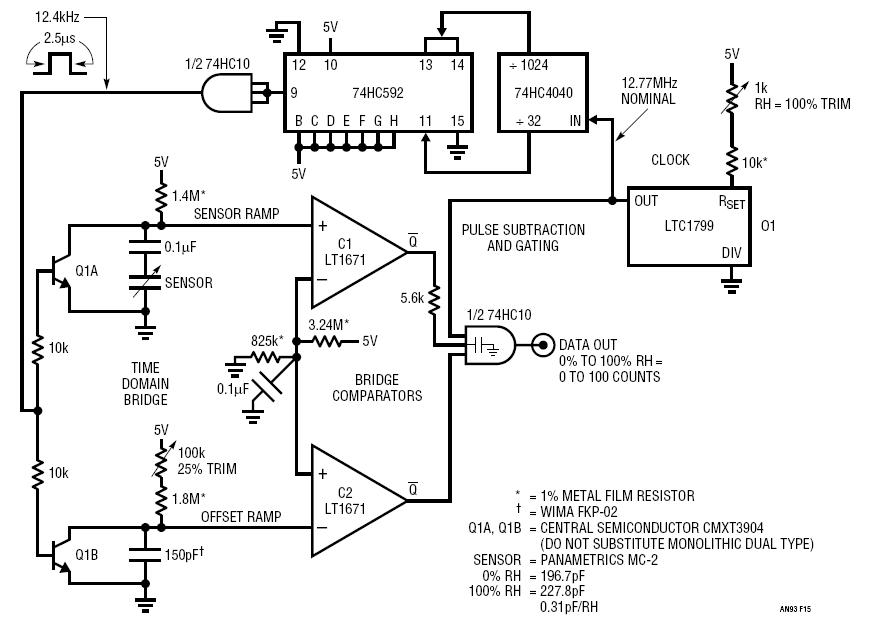

为了完成顺序延时的目的,必须确定50M和50.5M的时钟信号在什么时候才能同相对齐,通过图今4可以看到,当两时钟信号对齐以后,根据两者的周期差的原理,50M的时钟信号的1号位置的上升沿必定对应了50.5M时钟信号的高电平,而在同相对齐之前的一个时钟,即50M时钟信号的98号位置的上升沿必定对应50.5M时钟信号的低电平。根据这一推理,可以利用D触发器的原理,将50M时钟信号作为触发时钟信号,将50.5M时钟信号作为被触发信号,则当两时钟信号刚好达到同相对齐时,D触发器的输出端从低电平变成高电平;当两时钟信号刚好达到反相对齐时,D触发器的输出端则从高电平变成低电平。D触发器输出呈周期变化,周期T=20ns*99=1.980us,约为50OKHz的周期信号。该设计方法形同一个振荡电路,两时钟信号是振荡源。OSC_OUT作为振荡输出信号,上升沿表示同相对齐,下降沿表示反相对齐。设计结构和时序仿真结果如图4-5和4-6所示。

从图4一6可以看到,振荡输出信号的周期为1.9781us,与前面计算结果基本保持一致

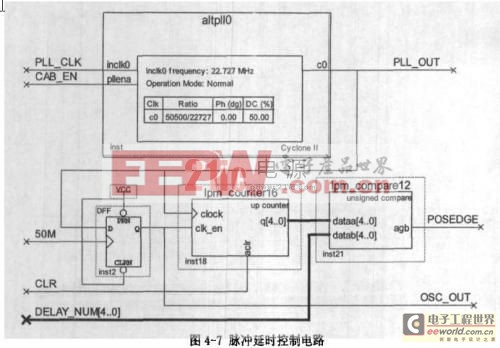

确定两个时钟信号的同相对齐点后,即可以实现步进延时的目的。由图4-4己知,要实现0.2ns的延时,就可以在对齐之后,通过对50.5M时钟信号进行计数,计数值为N,即被延时了0.2*N的时间间隔。为此可将图4-5中的D触发器的输出端作为计数器的使能控制信号,当D触发器的输出端由低电平向高电平变化时,计数器开始对50.5M的时钟信号计数,计数输出结果与预设次数做比较,当相等时,则表示达到预设的延时效果,此时比较器的输出状态即可被认为是输出脉冲信号的上升沿。脉冲延时控制电路如图4一7所示。

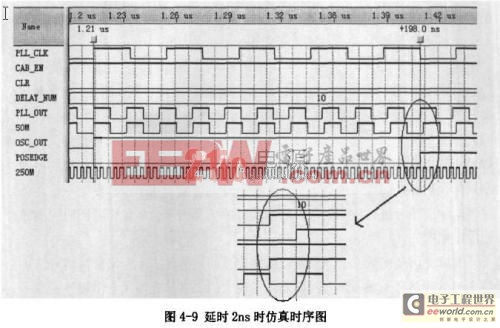

在图4-7中,比较器的输出端POSEDGE对应了图4-1脉冲产生电路中的D触发器的输入信号,从D触发器输出端即可产生时域反射测量所需的脉冲信号。图4-8、4-9给出了脉冲延时控制电路产生的0.2ns和2ns延时情况下的仿真时序图。

评论