雷达天线电源故障检测电路的设计

随着相控阵天线在雷达中的广泛使用,天线电源的故障检测变得越来越重要,相控阵天线的电源规模往往和收发(T/R)组件的多少成正比,当T/R组件多达上百个时,电源系统相对庞大,电源故障检测也较复杂,电源故障将直接导致T/R组件工作异常,因此设计一个完善的电源故障检测电路非常重要,它能实时对电源进行监测,及时发现故障,将故障定位到LRU,指导维修人员进行换件维修。

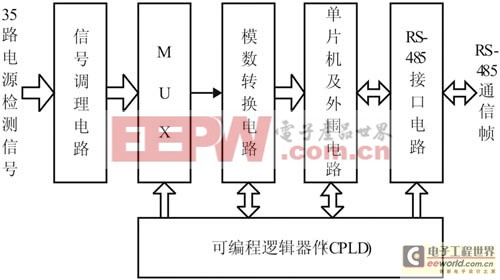

电源故障检测电路由硬件和软件两大部分组成,硬件组成框图如图1所示。信号调理电路对输入的35路电源检测信号进行滤波、分压及阻抗匹配,然后经过多路复用器(MUX)选择进入模数变换器(A/D),变换成数字量,单片机读入该数字量,与规定的上下限进行比较,判断该电压是否正确,最后生成单元级故障表,通过RS-485接口传送到上级进行进一步处理。

|

图1 硬件组成框图 |

电路设计

信号调理电路

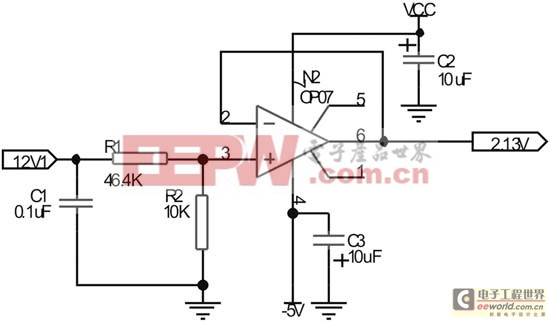

信号调理电路主要对输入的电源检测信号进行滤波、分压及阻抗匹配等处理。滤波的目的是滤除检测信号中的高频毛刺,通过试验可以看到,天线电源信号中常有幅度很大的干扰毛刺,如果不滤除可能会对器件造成损坏,或者影响检测精度。分压的目的是对检测信号的幅度变换,使其满足后级A/D变换器的输入要求,设计的关键是既保证信号的幅度不超出A/D的输入要求,又要尽量提高信号的分辨率。阻抗匹配电路是一个射极跟随器,目的是进行前后的阻抗匹配,提高检测的精度。图2是12V检测电压的调理电路。

|

图2 12V检测电压的调理电路 |

电容C1对高频毛刺进行滤除,一般取0.01μF,精密电阻R1和R2组成分压电路,为了减小对电源的影响,阻值应取千欧级,具体取值应参考12V的正常判定范围(10.3~14V)及A/D的满量程范围(0~2.55V),经过计算和权衡后,R1取46.4KΩ,R2取10KΩ,可以算出12V电压的欠压及过压门限值分别为:

欠压门限值:1.83V

过压门限值:2.48V

即输入12V电压经过分压后的正常范围应在1.83~2.48V范围内,否则判为故障。

多路复用电路

|

图3 MUX电路 |

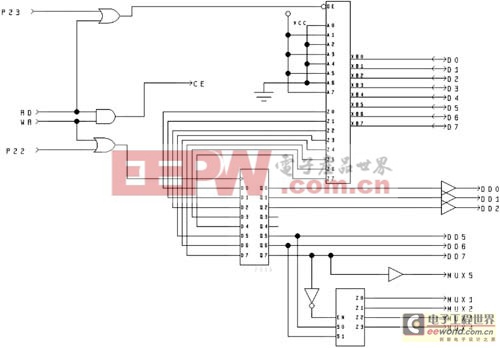

MUX电路如图3所示,主要功能是对35路被测电压进行选择,保证在某一时刻只有一路电压进入后级的模数转换电路进行数据转换。MUX电路共由两级组成,前级由五块八选一的多路复用器组成,35路被测电压经过调理后连接到这些MUX,图中只画出了两块的接线图,其余三块基本相同,后级由一块多路复用器组成,对前级输出的五路电压进行进一步的选择。图中信号MUX1、MUX2对前级芯片进行选择,信号DD0、DD1、DD2对前级的通道进行选择,信号DD5、DD6、DD7对后级通道进行选择,这些信号都是由CPLD产生,具体设计请参考2.5节CPLD内部逻辑电路的设计。

模数转换电路

|

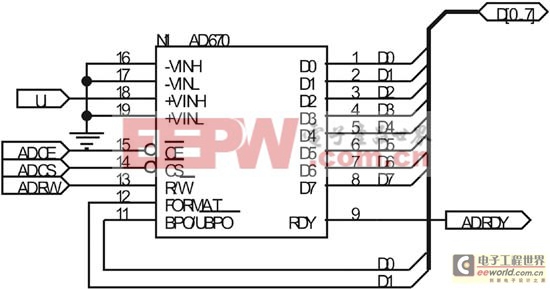

图4 模数转换电路 |

图4是A/D转换电路,主要功能是对输入的被测电压进行数据转换,转换的结果送单片机。A/D转换器件选用ADI公司的AD670,八位分辨率,10μs转换速度,可程控单极性或者双极性输入,单极性满量程输入范围为0~2.55V,双极性为-1.28~+1.27V,图中信号ADRDY为A/D转换完成信号,接单片机的I/O引脚,当ADRDY为低时,表示数据转换完成,在程序中通过查询该信号的状态判断A/D是否转换完成。信号ADCE、ADCS、ADRW分别是A/D的芯片使能、片选及读写控制信号,ADCE和ADCS低有效,分别接单片机的地址线P20和P21,ADRW为低时对A/D进行写操作,即写入控制命令,如单极性或者双极性操作等,ADRW为高时对A/D进行读操作,读出转换结果,该信号在CPLD中产生。

单片机及外围电路

|

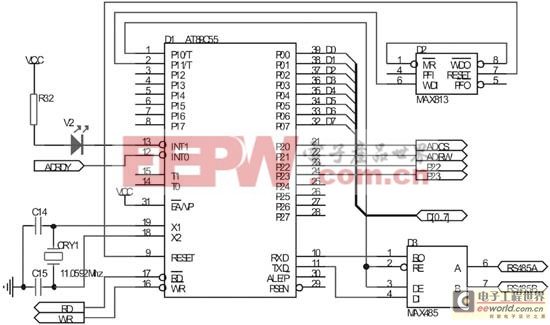

图5 单片机及外围电路 |

图5是单片机及外围电路,单片机选用ATMEL公司的AT89C55,内部带有20K字节的程序存储器,是整个故障检测电路的控制核心,它通过运行程序控制检测电路进行电压检测,将检测的结果进行初步处理,产生单元级故障表,送上级进行综合处理。集成电路D2(MAX813)是看门狗,主要功能是监视单片机程序的运行状态,如果程序跑飞超过1.6秒,看门狗就产生一个复位信号,对单片机进行复位,使程序重新进入正常步骤。集成电路D3(MAX485)是RS-485串行通信接口,它实现TTL电平与RS-485电平的相互转换,是检测电路与上级单元的通信接口。二极管V2是故障指示灯,当检测到电源故障时,点亮指示灯。

CPLD逻辑电路

图6是CPLD内部逻辑电路,CPLD选用的是LATTICE公司的ispLSI1016E,逻辑设计采用原理图输入法,主要功能是对MUX的通道进行选择、对A/D转换器进行控制及产生自检代码等。图中有三个主要器件:数据双向开关、数据锁存器、译码器。数据双向开关的OE为低时,数据A0~A7传向单片机的数据线D0~D7,该数据正常时是自检代码AAH,当OE为高时,单片机数据传向CPLD内部的锁存器,用来对多路模拟开关进行选择。端口地址译码使用了单片机的RD、WR、P22、P23引脚,还使用了单片机的P20及P21引脚,它们分别连接到A/D转换器CS和CE端,具体地址定义如下:

CPLD自检测地址:0x0700

通道选择数据锁存器地址:0x0b00

A/D转换器写地址:0x0c00

A/D转换器读地址:0x0e00

信号MUX1~MUX5是MUX电路的前级芯片选择信号,高电平有效;DD0~DD2是MUX电路前级的通道选择信号,取值范围是0~34,对应模拟通道的1~35;DD5~DD7是MUX电路的后级通道选择信号,取值范围为0~4,分别对应前级的五个MUX的输出信号。这些信号的产生过程是:单片机通过数据线D0~D7将通道选择数据及芯片选择数据送到锁存器,产生通道选择信号DD0~DD2及DD5~DD7,再将部分数据进行译码产生MUX的片选信号MUX1~MUX5。

|

图6 CPLD逻辑电路& DIY机械键盘相关社区:机械键盘DIY 相关推荐

技术专区 |

评论