小CPLD有大智慧 灵活应用在高频链逆变电源中

在本系统中,CPLD开发环境是MAXPLUSII,用Verliog对硬件进行编程。图6为时序仿真波形,其中CLK是CPLD系统时钟,vgs1是作为前端逆变电路和后端周波变换电路的同步信号,vgs1′是延迟a1角的信号,vgs1″是vgs1′与vgs1′异或得到的,它作为D触发器的时钟信号,PWM是软化同步后的调制信号,vgs11是S11开关管的触发脉冲。其中vgs1和vgs1″不作为输出信号要求输出,只是为仿真调试方便列出。

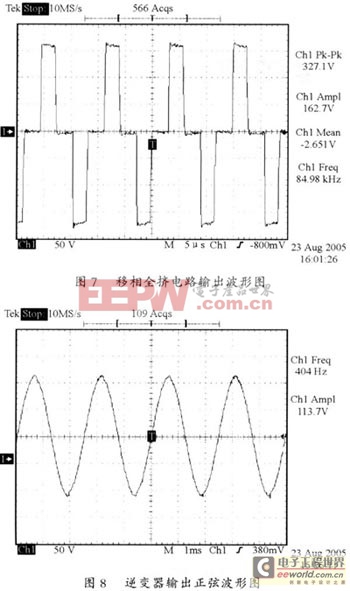

采用上述主电路结构和控制方式,研制了输出功率350W,输出频率400Hz,输出电压115V,开关频率100kHz的原理样机。图7给出的是前端移相全桥的输出波形,测试点是高频变压器的副边,波形与原理波形一致。因为高频变压器漏感的缘故,开通瞬间存在振荡电压尖峰。

图8是逆变器的输出波形,通过两级LC滤波,波形谐波畸变很小,满足指标要求。

5 结语

实现高集成度,高灵活性,具有较高的参考价值。

评论