卷积码+QPSK的中频调制解调系统的FPGA

在无线数据传输中,由于信道中的噪声干扰,在接收端会引入一定的误码率(Bit Error Rate,BER)。高质量的数据业务要求较低的BER。为了达到较低的BER,经常采用信道编码技术。卷积编码和Viterbi译码是广泛使用的信道编码技术,具有一定的克服突发错误的能力,可以降低信道的误码率,带来很高的编码增益。信道编码的引入在提供纠错能力的同时,还扩展了信号的带宽。为了保证频带的利用率,本文采用QPSK调制方式,使数据调制在中频载波上,实现数据的可靠传输。

本文所述的中频调制解调系统具有以下特点:

(1)所有算法(编码、调制、解调和译码)都是在Xilinx公司的FPGA芯片中实现的,结构简单,体积小,功耗低。

(2)具有很好的实时性。对于1Mbit/s以上的数据速率,译码延迟不超过0.1ms。

(3)模块化的设计使得系统具有一定的兼容性,只需要修改少量程序,即可实现各种卷积编码和不同的调制中频。

1 系统总结构及硬件设计

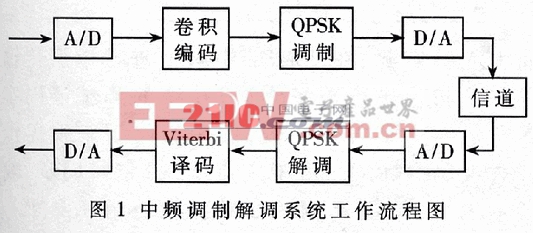

图1是中频调制解调系统的工作流程图。在发端,数据通过A/D转换器采样后进入FPGA,在其中完成(2,1,7)卷积编码和QPSK调制后通过D/A转换器输出。在收端,接收到的信号通过A/D转换器采样后进入FPGA,在其中完成QPSK解调和Viterbi译码后通过D/A转换器输出。

2 系统的FPGA实现

系统主要分为编译码和调制解调两大部分,下面分别叙述这两部分的原理及设计。

2.1 卷积编码与Viterbi译码的FPGA实现

2.1.1 (2,1,7)卷积编码

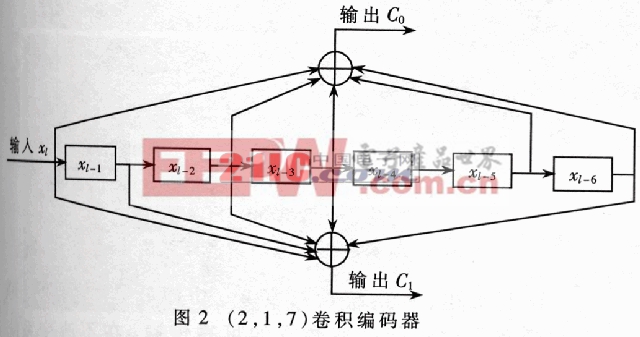

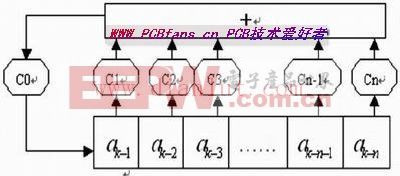

典型的(n,m,k)卷积码编码器是指输入位数为m、输出位数为n、约束长度为k的卷积码编码器,其编码速率为m/n。一个(2,1,7)的卷积编码器如图2所示,可用六个移位寄存器实现。

2.1.2 Viterbi译码

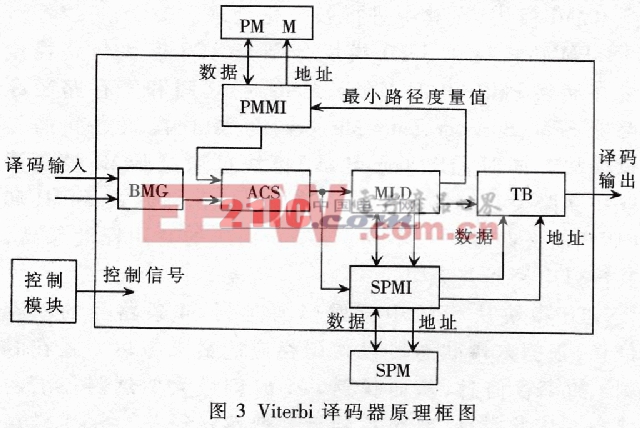

由Viterbi算法的基本原理可得典型的Viterbi译码器,如图3所示。

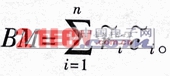

分支路径度量产生单元BMG(Branch Metric Generate)用于产生接收序列与状态转移分支上编码输出数据之间的距离。令长度为n的接收信号为R=(r1,…rn),与之相应的发送信号为C=(c1,…cn)。因为具有最小欧式距离的路径也就是具有最大相关的路径,所以定义分支路径上的度量为: 由于此分支路径度量没有平方运算,所以可将状态转移分支上的编码输出数据存储在查找表内,这样只需进行加减和查表运算,大大减小了实现的复杂程度。以上计算公式中数值为连续值,而本设计采用的是软判决译码器,故只需对输入的接收信号进行均匀量化即可(量化比特数为q)。

由于此分支路径度量没有平方运算,所以可将状态转移分支上的编码输出数据存储在查找表内,这样只需进行加减和查表运算,大大减小了实现的复杂程度。以上计算公式中数值为连续值,而本设计采用的是软判决译码器,故只需对输入的接收信号进行均匀量化即可(量化比特数为q)。

相关推荐

-

-

xiaohua | 2002-09-24

-

-

sandman555 | 2005-02-05

-

-

sandman555 | 2005-02-05

-

-

-

-

sandman555 | 2005-02-05

-

-

-

-

herbertwj | 2004-08-15

评论