利用低成本FPGA设计下一代游戏控制台

高速的芯片至芯片互连

FPGA通过高速的芯片至芯片互连技术与GPU和CPU连接,这些技术包括HyperTransport、PCI Express或串行RapidIO。串行RapidIO和PCI Express是串行而非并行技术,即串行地发送数据,并通过LVDS以数据包的形式恢复数据,而不是一次恢复一位。从并行到串行接口的转换系统可用较少的线路达到同样的高速数据速率。

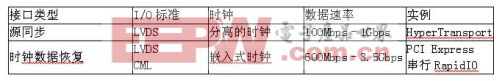

源同步和时钟数据恢复接口

HyperTransport是一个源同步接口,而PCI Express和串行RapidIO采用时钟数据恢复(CDR)技术,如下表所示。对于源同步接口而言,传送方提供数据和差分时钟,这样就能较容易地在高达700Mbps的数据速率捕获数据。

源同步和时钟数据恢复接口。

当数据速率超过700Mbps时,数据通道之间的偏移成为数据有效窗的重要部分,特别是对宽数据通道而言。有些FPGA具有自动对齐功能,能够针对源同步接口管理数据偏移,从而有助于它们达到超过800Mbps的LVDS数据速率(有些情况下高达2Gbps)。

对于CDR接口而言,并没有提供额外的差分时钟。取而代之的是时钟包含在串行数据包中,必须从数据中恢复出来。因此,对于CDR来说时钟偏移不是一个问题,这与源同步不同。利用SERDES高速串行地发送数据包,CDR接收器将对数据本身锁定相位以取得时钟。

对于CDR而言,在高速情况下,SERDES抖动是主要问题。抖动是指期待数据传输的位置发生了变化,使得难以准确地接收到数据包。如图3所示的眼图,抖动使得围绕眼睛的黄色带的宽度发生变化,图中用红色表示。

图3:CDR眼图。

有些抖动是随机的,但大部分抖动是确定性的,是由于其它信号以及靠近数据信号的半导体元件的开关操作引起,或者是由数据模式的特性、传输的不平衡上升及下降时间所引起。

评论