一种MPEG4视频压缩和传输系统

在重要场所安全监控或工业现场控制系统中,直观、方便且内容丰富的视频实时采集是信息采集的重要部分,也是人们关注的应用技术热点。由于高精度实时视频信息量巨大,在传输时需丢弃大量数据帧,否则必须压缩。最常用的是软件压缩法,但对复杂的压缩格式编程工作量大、设备要求高、应用受限制。而硬件实现法,采用专用芯片按即定格式高速压缩视频,实时性好,可靠性高。

本文介绍的视频数据实时压缩和传输系统,采用可编程视频采集芯片采集模拟视频,通过MPEG4/2/1专用编码芯片对采集后的数字视频数据进行编码压缩,生成MPEG4码流,微控制器的在片以太网卡端口外接网络物理层芯片,MPEG4码流由此输出到视频终端PC机,整个系统由微控制器调度管理。终端PC上应用程序播放视频进行监控。

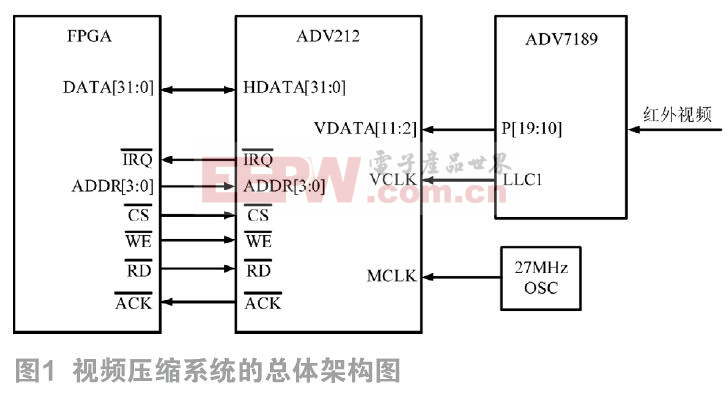

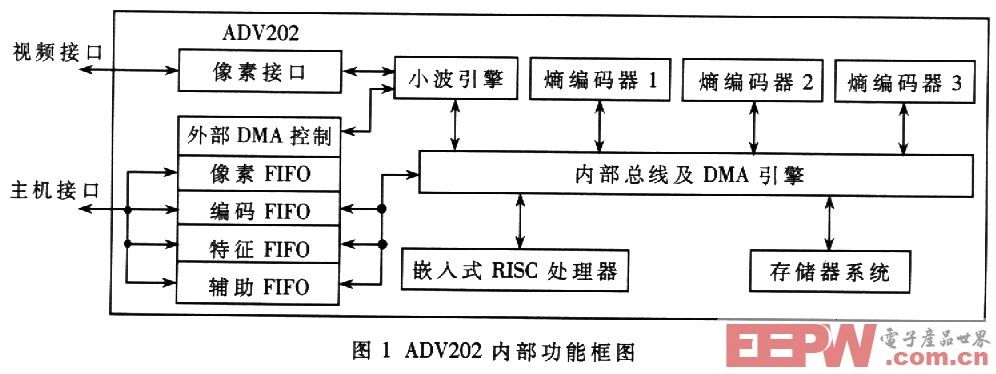

2 系统总体结构

系统主要包括两部分。一是数字视频数据采集和编码子系统。二是视频码流以太网发送子系统。此外还有电源子系统、JTAG调试子系统等。图1所示为系统框图。

视频采集芯片选用Philips公司SAA711lA。该芯片的工作时钟为24.576MHz,由此1/2行输出锁定时钟LLC2为13,5 MHz。设定输出数据色彩格式为4:2:2,输入模拟视频采用S-Video端子的PAL格式视频信号,分辨率为720X 576,每秒25帧。设定抗混叠滤波、AD转换、自动钳位、自动增益变换、PAL和NTSC制式之间自动切换等功能。微控制器通过12C总线初始配置SAA711lA。

数字视频数据编码压缩工作由INTIME公司设计的IME6410单片视、音频MPEG4/2/1码流压缩引擎完成。同SAA711lA一致,一帧图像分辨率设置为720X 576,输入数据色彩格式为4;2:2。IME6410具有符合工业标准的视频数字编码器无缝接口,16b的复合主机接口,分别用来与视频采集芯片和微控制器芯片通信。微控制器通过主机接口实现IME6410的初始配置,也由此接收压缩得到的视频码流。

微控制器是本系统的核心部件,选用ATMEL公司的基于ARM920T核的32b微控制器ATglRM9200。他包含丰富的系统接口和外围应用接口,如10/100BaseTMAC和主机接口HDI,可灵活配置片上和片外存储器,向各种的高速计算应用提供了一个单片解决方案。在系统中的主要作用是在系统上电时配置其他芯片的功能寄存器,正常工作状态下调度控制系统工作,存储编码得到的MPEG4码流,通过在片以太网端口控制物理层芯片发送码流。

以太网发送的物理层芯片选用REALTEK出品的单片、单端口10/100 M以太网物理层芯片RTL8201。RTL8201应用与在片MAC通信的独立媒体接口MII。PHYAD0-PHYAD3置高,PHYAD4置低,则物理层地址为0x10。芯片符合IEEE802.3/802.3u规则。标准的IEEE802.3数据帧由以下几个部分组成:前导位(preamble)、帧起始位(SFD)、目的地地址(destination)、来源地址(source)、数据长度(1ength)、数据(data)、帧校验字(FCS)。数据字段大小可从46B到1 500B,如一组要传送的数据不足46B,就用零补足;超过l 500B时,需要拆成多个帧传送。数据在发送之前按此格式进行封装。

系统独立运行的程序存储在FLASH中,采用ATMEL公司生产的AT49BV322A,容量为2MXl6b。系统上电后,首先进行程序的自举加载,程序加载到SDRAM中运行,进行系统的初始化,随后进入正常的工作状态。运行程序和存储码流要求较大的动态存储空间,采用SAMSUNG公司的K4S561632E SDRAM,容量为16 MXl6b。

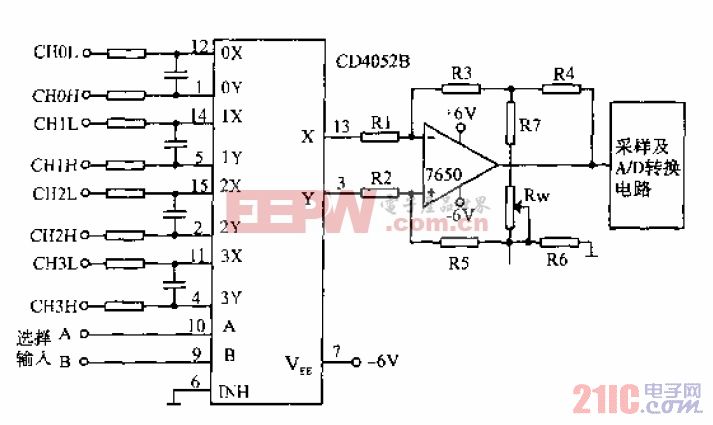

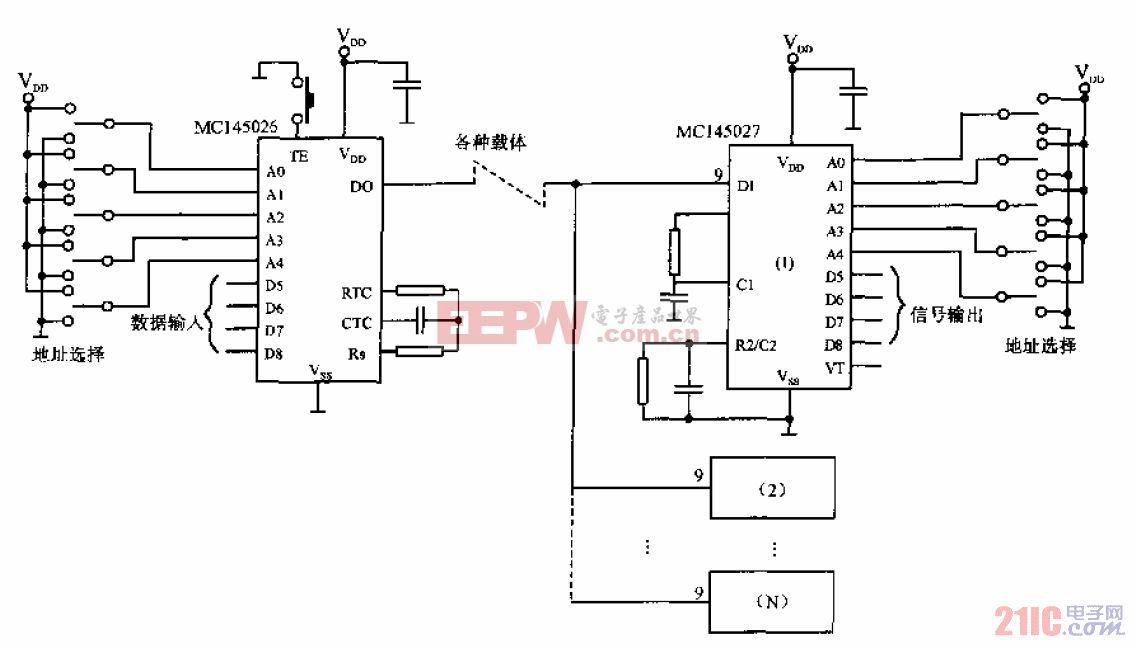

3.数字视频数据采集和编码子系统

子系统硬件电路图如图2所示。

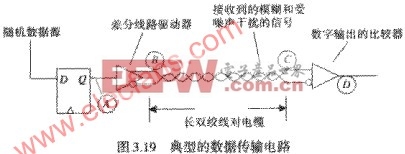

SAA711lA的A1模拟输入口与模拟摄像头输出端连接,向视频处理芯片传送模拟视频信号。IME6410具有符合工业标准的视频数字编码器无缝接口,可方便地与SAATlllA通信。SAA711lA对模拟视频信号采样处理后得到的数字视频信号按1/2行输出锁定时钟LLC2从VP00一VP015引脚送到IME6410,数据在LLC2上升沿时有效,IME6410在PCLK引脚接收的象素点输入时钟信号LLC2的上升沿抓取VD端口数据,如图3所示。SAA711lA可分离场同步脉冲和行同步脉冲,每视场的数字视频信号有效之前,SAA71llA会输出场同步脉冲,并使能垂直参考信号VREF置高;而在每行信号有效之前,也会输出行同步脉冲,并使能水平参考信号HREF置高。奇偶场识别信号RTS0与奇、偶场指示信号FIELD引脚连接,高电平指示奇场,低电平指示偶场。IME6410首先判断奇、偶场,随后当VREF和HREF有效时何时开始接收一行的数据,当一行数据接收完毕后HREF被置低,一场数据接收完毕后VREF被置低,避免在黑电平期间接收无用数据,同时翻转奇偶场识别信号电子。IME6410接收数据的同时,芯片内部视频处理器对数据进行MPEG4编码并输出到缓冲器。

IME6410通过主机接口和AT91RM9200通信,AT91RM9200将IME6410的寄存器、存储空间等资源作为SRAM寻址访问。IME6410通过与AT91RM9200的SRAM端口数据线DO-D15连接的主机接口数据线HD0一HDl5向AT91RM9200传送编码压缩后得到的MPEG4码流。AT91RM9200由SRAM选通线NCS7选通IME6410芯片,其存储空间在AT91RM9200寻址空间中地址段为0X80000000到0X8FFFFFFF。地址线A0~A4与IME6410的主机口地址线HA0~HA4连接,寻址访问IME6410的寄存器,其13个内部寄存器均为16B,偏移地址从0x00到0xle。通过对ADDR,DATA和CONTROL寄存器的读写等一系列操作,可以访问IME6410系统存储空间。IME6410数据流缓冲器标志信号NFULL从配置为通用I/O引脚的PC20输入,当缓冲器满或丰满时,NFULL引脚置低提示AT91RM9200提取编码数据。编码后视频数据读过程和IME6410与主机通信过程具体由AT91RM9200读信号NRD和写信号NWE控制。

评论