Ports模式下CY7C68013和FPGA的数据通信

引言

本文引用地址:https://www.eepw.com.cn/article/21387.htm通用串行总线(usb)具有快速、双向、大批量传输、廉价以及可实现热插拔等优点,cypress公司的fx2系列芯片之一cy7c68013是最早符合usb2.0标准的微控制器,集成了符合usb2.0的收发器、串行接口引擎(sie)、增强型8051内核以及可编程的外围接口,实现基于usb2.0的接口数据通信,cy7c68013可配置成3种不同的接口模式;ports(端口模式)、gpif master(可编程接口模式)和slave fifo(主从模式),其中,后两种模式利用其内部集成的可以独立于微处理器而自动处理usb事务的硬件(usb核),数据的传输通过执行usb本身的协议来完成,微处理器可不参与数据传输,从而使数据的传输速率大大地提高,同时也简化了固件代码的编写。后两种方式由于克服了微处理器这个带宽"瓶颈",因而广泛应用于大批量的数据传输,如图像、视频等信号的采集。

而对前一种ports(端口模式),文献中介绍较少,作为一种最基本的数据传输方式,其数据传输主要由固件程序完成,需要cpu的参与,因此数据传输速率比较低,适用于传输速率要求不高的场合,而且由于fx2内部集成有8051内核,对一个刚从单片机的开发过渡到usb开发的工程人员来说,也不失是一种有效的数据传输方式,现以一个工程开发的实例来详细说明一下在ports模式下如何实现数据一双向传输。

1 设计要求

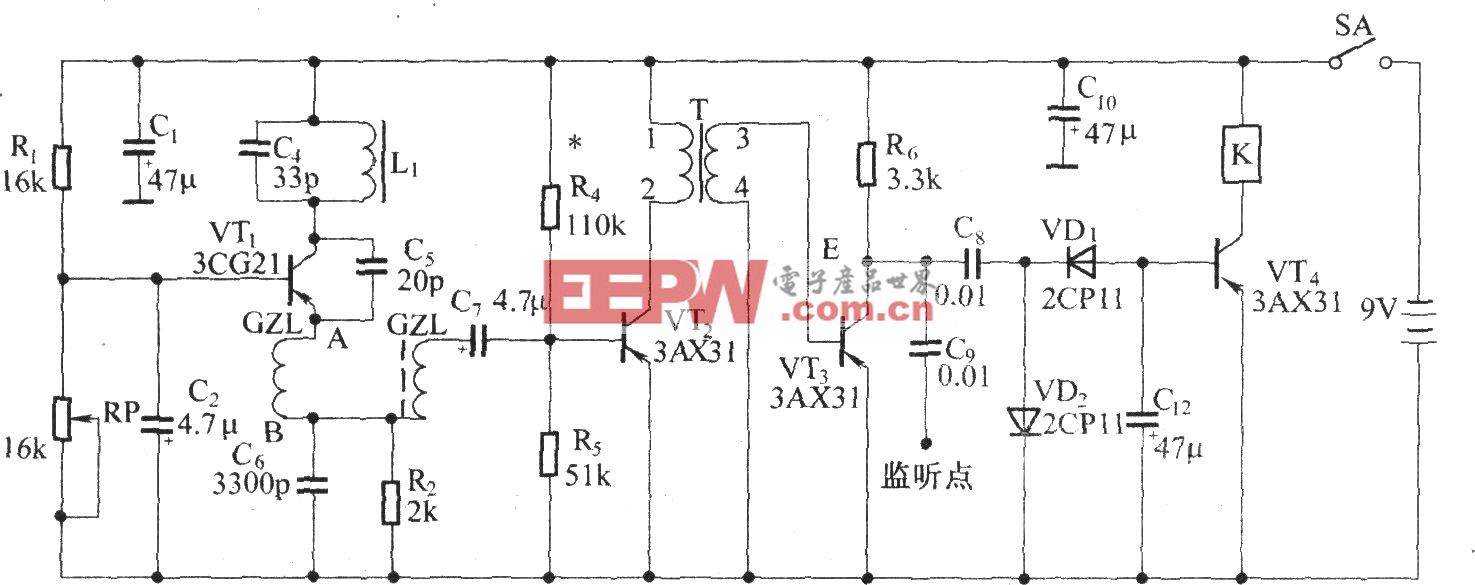

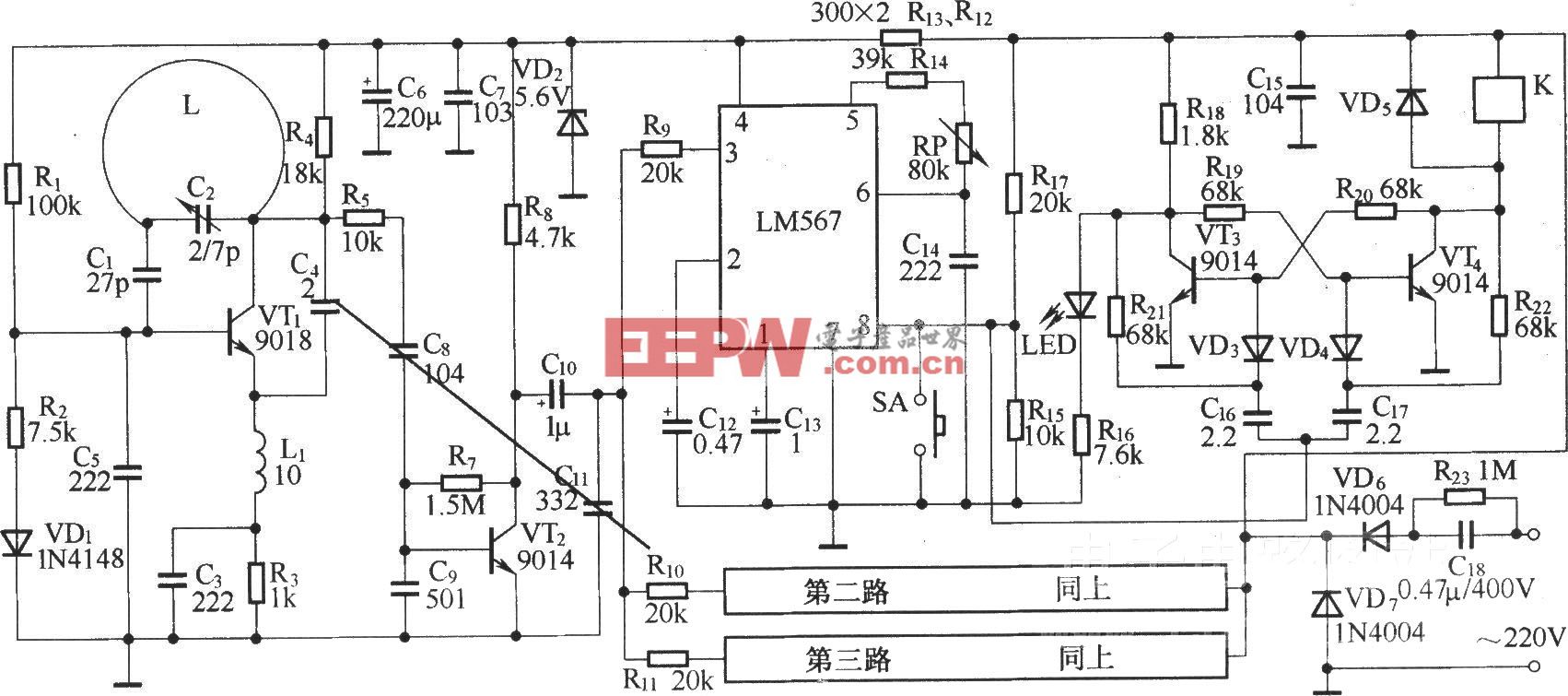

主机通过usb接口以4kb/s的速率分别向两个通道发送数据序列,并由外设的d/a转换器完成数据的转换,同时,由外部的两个a/d转换器以400kb/s的采样率完成数据的采集,采集后的数字信号也经usb接口传送至主机存储,其中,usb接口芯片采用cypress公司的cy7c68013,fpga采用altera公司的ep1c6q240c8,图1为其数据的多路传输系统框图。

2 usb

数据多路传输硬件

2.1 ez-usb fx2 cy7c68013

ez-usb fx2 cy7c68013支持usb2.0数据传输,其内部结构及功能在其他文献已有详细的介绍,现针对此芯片在本电路的作用进行简要的说明,在设计中主要利用cy7c68013的ports接口模式完成多路数据的传输,usb和fpga之间数据和状态的传输由cy7c68013的ioa接口完成,iob接口中的iob0-iob2口线作为usb和fpga之间的控制线。cy7c68013内部的ep2端口设置为512字节双缓冲、out、块传输,作为主机向外设发送数据的缓冲区;ep6端口设置为512字节双缓冲,in、块传输,作为外设向数据传送数据的缓冲区。

2.2 fpga芯片ep1c6q240c8

fpga采用altera公司的cyclone 芯片ep1c6q240c8。在这里fpga的作用有3个:其一,给两路d/a转通道各分配两个128×8位的ram区,作为从主机向外设发送数据的缓存。其二、给两路a/d转换通道各分配两个512×8位的ram区,作为从外设向主机传送数据的缓存,由于两路数据的传输和采集共用一个8位数据总线,因此,数据总线要针对不同的接收和发送来回切换,因而每个通道的两路分别采用两个ram块,起到双缓冲作为,以防传输时数据"溢出"的。其三,由于数据总线要针对不同通道来回切换,控制切换的过程由状态寄存器来完成,因此,要在fpga内部设置一个状态寄存器,所设置的状态寄存器仅包含两位,分别标识两个通道的数据ram的"满"或"空"的状态,以确定当前应该为哪一个通道发送或接收数据。

3 通信协议的制定

采用cy7c68013的ports模式实现数据通信,与fifo和gpif模式不同,后两种模式在数据传输方面主要由usb核完成,所需的控制信号由cy7c68013自身来提供。而对于ports模式,控制信号没有专用的口线,那么就必须用其他通用的i/o接口来完成,在此,采用iob0-iob2作为usb和fpga之间的控制线,由于自定义的3条线是通用口线,没有实际的意义,因此在usb和fpga之间首先要制定两者的通信协议,即给这3条口线赋以实际的功能。

ale(iob0):例如ale的上升沿,通过ioa端口向fpga传送控制指令,例如,当ioa=01h时,表示系统开始工作,a/d和d/a转换器开始启动。当ioa=88h时,表示转换结束,fpga将不再接收或发送数据,当ioa=02h时,表示cy7c68013将读取fpga内状态寄存器的内容,由读取两状态标志位的0或1,来判断两个通道内的4个数据缓冲器的"满"或"空"状态,若d/a通道的任一个数据缓冲区为"空",则由fpga向状态寄存器的第一个状态标志位内填1;否则填0;同理,若a/d通道的任一个数据缓冲区为"满",则由fpga向状态寄存器的第二个状态标志位内填1;否则填0;当ioa=03h时,表示主机将通过usb向d/a通道发送转换数据,每次发送256个字节,前128字节为d/a转换的1通道,后128字节为2通道,当ioa=04h时,表示主机将要接收由a/d通道传送来的数据。

rd(iob1):利用rd的上升沿通过ioa端口读取d/a转换器转换来的数据。

wr(iob2):利用wr的上升沿通过ioa端口向a/d转换器发送由主机传送来的数据。

4 软件的实现

usb与fpga在ports模式下数据的传输,由于是由cy7c68013内部的cpu核来实现的,因此,对固件程序的编写显得比较重要,总的来说,固件程序的编写有两种方式:一是由于cy7c68013的内部集成有增强型8051内核,对熟悉8051汇编语言的用户来说,可以直接利用会汇编语言编写高效的固件代码;二是cypress公司ez-usb fx2系列配套有现成的固件程序框架函数,用户需要时,只需添加相应的用户程序即可。当然,用户程序中的数据通信的实现也就是如何完成通信协议的过程。

在此,采用后者来完成cy7c68013和fpga的数据通信,实现数据通信功能的部分软件代码如下(以下代码均可写在框架函数void

td_poll(void)内):

5 总结

cy7c68013和fpga的数据通信中,采用基本的ports接口模式,利用自动指针方法,通过数字示波器的观察,完成1kb的传送,大约需要750μs。与另外两种模式相比,虽然数据传输的速度较低,但作为一种数据传输模式,尤其对刚从单片机开发过渡到usb开发的工程人员来说,也不失为一种有效的开发方式。

评论