CMOS工艺复接器模块中选择器的设计

1 引言

众所周知,组织通信的一个缺点是他需要的信道带宽比较大,而光纤中数据传输比特率理论上可以达到tb/s(1015b/s)数量级,光纤传输系统的产生极大地满足了数字时代大量信息高速传输的需要。自1962年激光二极管的研制成功和1970年低损耗光纤问世以来,光纤通信技术得到了迅速发展。以光纤为传输信道的局域网lan(特别是千兆以太网),城域网man,广域网wan,异步传递模式atm和同步数字体系sdh等一系列高速数字通信标准相继建立[1]。光纤传输通信逐渐成为通信领域的一种重要的传输方式。

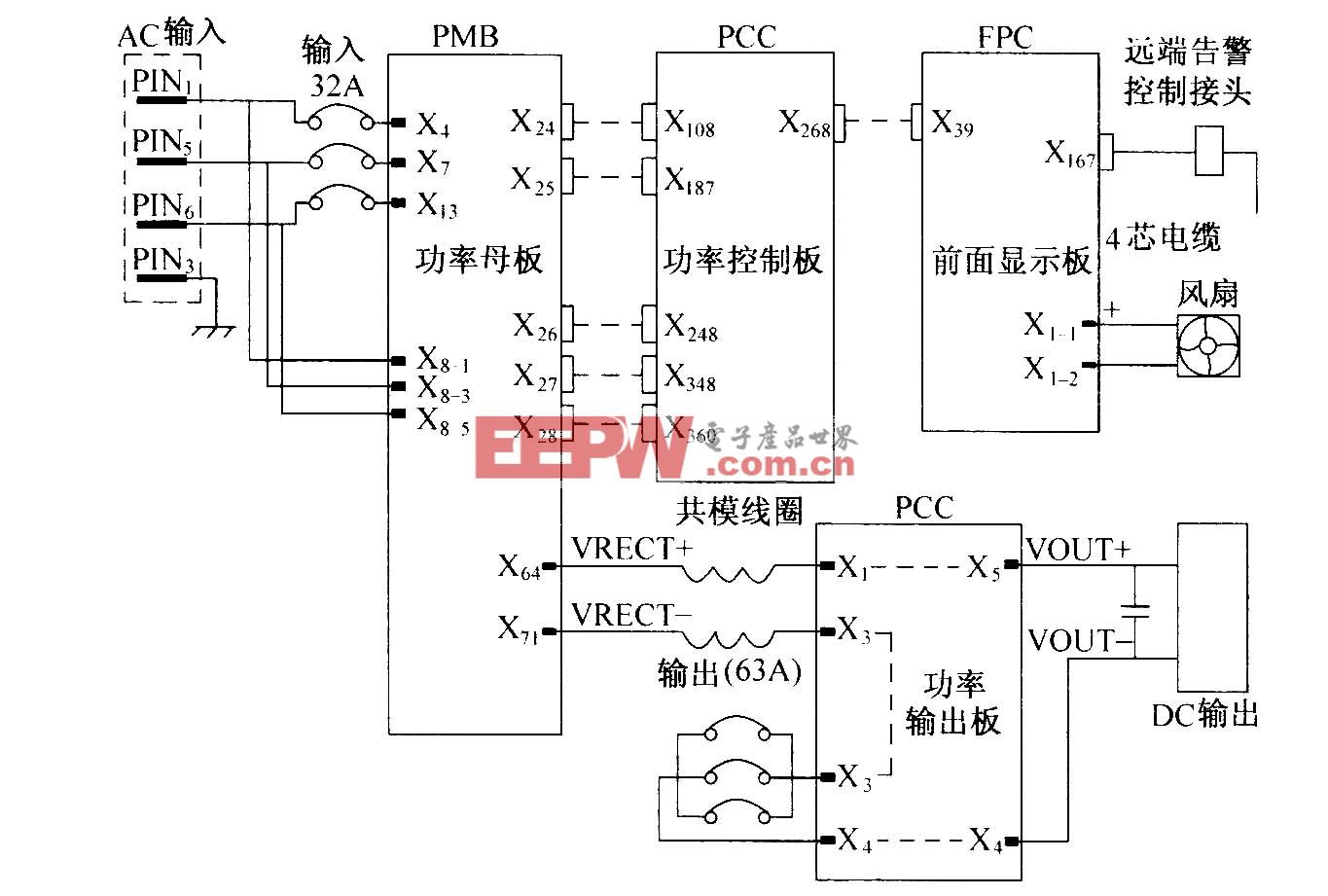

本文引用地址:https://www.eepw.com.cn/article/20894.htm在光纤传输系统中,复接器将多信道传输的多路低速信号合成一路高速信号,激光驱动器驱动激光二极管将合成后的信号转换成光信号通过光纤进行传输。复接器的使用提高了光纤信道容量的利用率,是实现高速数据传输的关键电路之一。图1为高速2:1复接器的框图,两组输入数据d1和d2经过触发器后最终由选择器将他们合并成一组数据输出,选择器的逻辑功能正确与否和性能直接决定了复接器模块的逻辑功能正确与否和整体性能。

2 选择器的电路设计

数据选择器也叫多路开关,其功能是从多路输入数据中选择其中一路送到输出端。数据选择器的工作原理可以简述如下:如果一个与门的某个输入端加数据信号,门的其他输入端加选通信号,当其选通信号都为高电平时,则与门的输出即等于该输入数据信号。此时,可以说该输入信号已经被选中并送到输出端。

图2是以mos晶体管差分对为单元的scfl2:1数据选择器基本电路。逻辑运算部分有3个差分对管,分上下两层,时钟信号输入下层的差分对管,两路差分的数据连接上层的两个差分对管,scfl选择器的核心是工作在限幅区的差分放大器。图2中m5和m6工作在开关状态,由系统的时钟控制。当ck为高电平,ckn 为低电平时,m5导通,m6截止,m1和m2工作在限幅区,m3和m4无效。数据d1,d1n,通过m1和m2传输到d0,d0n。反之,当ck为低电平,ckn为高电平时,m6导通,m5处于截止状态,m3和m4工作,m1和m2无效。数据d2,d2n通过m3,m4传输到d0,d0n。

3 参数调整方法

电路参数的调整是电路设计中重要而又烦琐的工作。如何才能快速、准确地进行参数调整,这里介绍一种作者从实际的工作中总结出来的,称之为观察分组法的参数调整方法。

选择器电路参数在调整过程中要注意晶体管的对称性。因为scfl结构的许多优点都来自他的对称性。对于一个待调整的子电路,首先观察他的电路结构,将晶体管按功能和结构分成若干组。在参数调整时,每组晶体管的参数应尽量保持一致,这样既满足了电路结构的要求,又减少了工作量,而且也是版图设计的需要。在版图设计中要尽量保持版图的对称性,这就体现在参数调整中,需要注意相同功能和结构的晶体管参数的一致性。每次只调整一组晶体管的参数。当所有组的晶体管参数都达到最佳状态后,再进行总体的调整,使子电路的性能达到最佳。另外在参数调整过程中要有规律性,从小到大或者从大到小,每次的参数及其结果要记录下来,这样,可以清楚地看出晶体管参数对电路性能的影响,避免重复劳动,节省了大量的时间。

观察图2,scfl选择器的电路结构,可以看出,逻辑运算部分共有3个差分对管,分上下两层。根据差分结构的特点,构成差分对的2个晶体管的参数应该保持一致,m1和m2,m3和m4,m5和m6分别分为一组,再看上层的两个差分对,他们在时钟的不同阶段分别实现相同的功能,所以可以将m1,m2,m3和m4合并为一组,有源负载m9和m10可以分为一组,构成源极跟随器的m7和m12,m8和m13可直接影响输出信号的中心电平,为了使输出信号d0,d0n的中心电平保持一致,这里将m7和m8,m12和m13分别分为一组。

这里以构成源极跟随器的m7,m8这组晶体管为例简单介绍参数的调整过程。改变这两个管子的宽长比可以改变源极跟随器的输出信号幅度。图3分别是w7=w8=4u和w7=w8=16u,他们的长都为0.6u时输出信号的幅度变化。从图中可以明显看出,m7,m8的栅宽变大,栅长不变,输出信号的幅度也变大。了解这一变化趋势后,就可以根据设计的中要求来调整m7和m8的栅宽,使输出信号的幅度达到合适的范围。其他组的元件参数也是这样根据要求逐一进行调整,最终达到电路的设计要求。

4 仿真结果

仿真采用了 csmc-hj0.6μm cmos工艺的器件参数库,环境温度为27℃。输入的两组数据信号一组全为1,另一组全为0,输入155.52mhz的正弦信号作为时钟信号,如图(4)所示。仿真结果如图4(b)所示,分析可知,选择器的输出信号应为0,1相间的序列。

5 结语

设计中采用了源极耦合场效应管逻辑电路,并采用0.6μm cmos工艺来实现了选择器,在参数调整过程中总结出一种新的方法-观察分组法,从仿真结果看,该电路实现了数据选择的功能,电路的参数也都达到最优。

评论