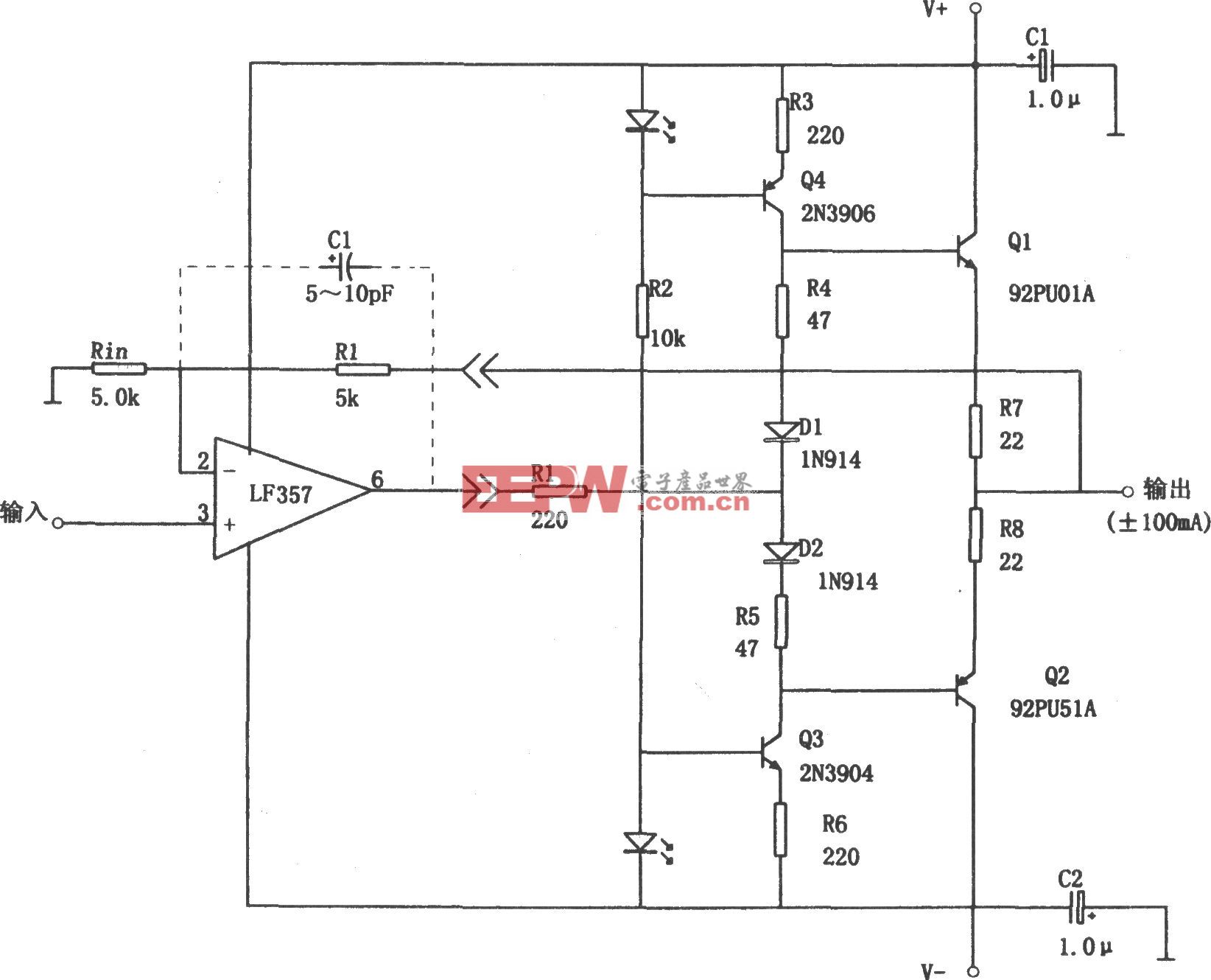

DAC及其缓冲器有助于提升系统性能与简化设计一

乘法DAC的R-2R梯形电阻设计用于将电流平均分配至各个引脚。这就要求总接地电阻(从各引脚顶部看)完全相同。这可以通过调节开关来实现,其中,各个开关的大小与其导通电阻成比例。如果一个引脚的电阻发生变化,则流过该引脚的电流将发生变化,结果导致线性度误差。VIN不能大到会使开关关闭的程度,但必须足以使开关电阻保持低位,因为VIN的变化会影响VGS 从而导致导通电阻发生非线性变化,如下所示:

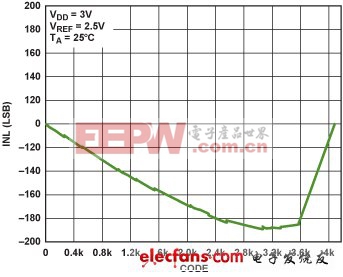

导通电阻的这种变化会使电流失衡,并使线性度下降。因此,乘法DAC上的电源电压不能减少太多。相反,基准电压超过AGND的值不得高于1V,以维持线性度。对于5V电源,当从1.25V基准电压变化至2.5V基准电压时,线性度将开始下降,如图7和图8所示。当电源电压降至3V时,线性度将完全崩溃,如图9所示。

图7. INL of IOUT 乘法DAC在反相模式下的INL,( VDD = 5 V, VREF = 1.25 V)

图8. INL of IOUT乘法DAC在反相模式下的INL(VDD = 5 V, VREF = 2.5 V)

图9. 乘法DAC在反相模式下的INL( VDD = 3 V, VREF = 2.5 V)

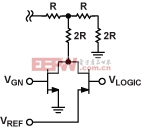

为了减少这种影响,AD5541A采用互补NMOS/PMOS开关,如图10所示。现在,开关的总导通电阻来自NMOS和PMOS开关的共同贡献。如前所示,NMOS开关的栅极电压由内部逻辑控制。内部产生的电压,VGN,设置理想栅极电压,以使NMOS的导通电阻与PMOS的相平衡。开关的大小通过代码调节,以使导通电阻随代码调节。因此,电流将上下调节,精度将得以维持。由于基准输入的阻抗随代码变化,因此,应通过低阻抗源驱动。

评论