DSP+FPGA的机载总线接口板研究(二)

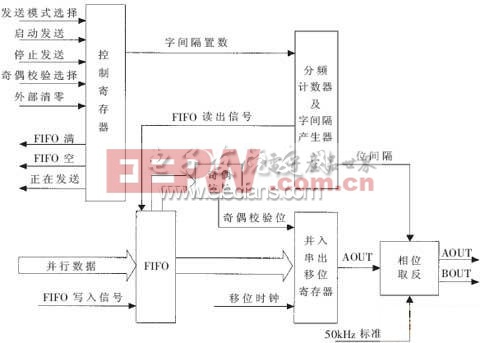

图4 发送模块结构框图

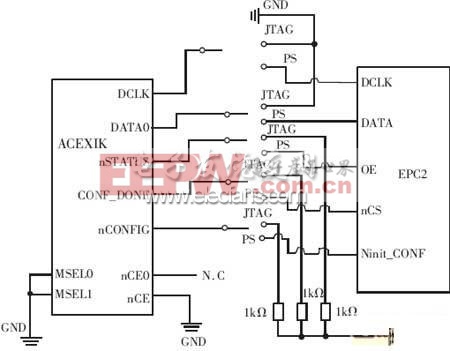

FPGA内部结构是基于SRAM的,因此需要一片配置芯片固化内部逻辑。为了便于调试,采用JTAG模式和被动串行模式(PS)两种配置模式,调试时使用JTAG模式直接将逻辑写入FPGA内部,调试好后再用PS模式将程序写入配置芯片。通过对FPGA和配置芯片上的引脚进行跳线,可选择不同的配置方式。跳线电路如图5所示。

图5 FPGA配置跳线设置

FPGA作为DSP的一个I/O外设,必然要对它的寄存器地址统一编址。在此将FPGA编址在DSP的I/O空间。由于FPGA的接收通道和发送通道是共用DSP的16位数据线的,故接收通道和发送通道的数据寄存器可以占用一个地址。表1是FPGA各通道寄存器分配的地址。

表1 FPGA内部各通道寄存器地址

3.3 DSP与FPGA及外部设备的通信

DSP(digital signal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。其工作原理是接收模拟信号,转换为0或1的数字信号。再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

评论