多裸片芯片设计中凸点与硅通孔的高效规划方案

近年来半导体行业发展迅猛,尤其是高性能计算、人工智能和先进汽车系统的需求持续攀升,传统单裸片芯片设计已难以满足当下的功耗、性能、面积(PPA)指标要求。为此,工程师们开始采用多裸片架构,将多个小尺寸裸片集成在单个封装中。该架构虽提升了芯片的可扩展性与性能,却也带来了新的挑战,其中互连规划问题尤为突出。而实现不同裸片间的通信,凸点与硅通孔(TSV)的高效规划,是多裸片集成过程中至关重要的环节。

(图 1:基于电子表格的凸点规划示意图)

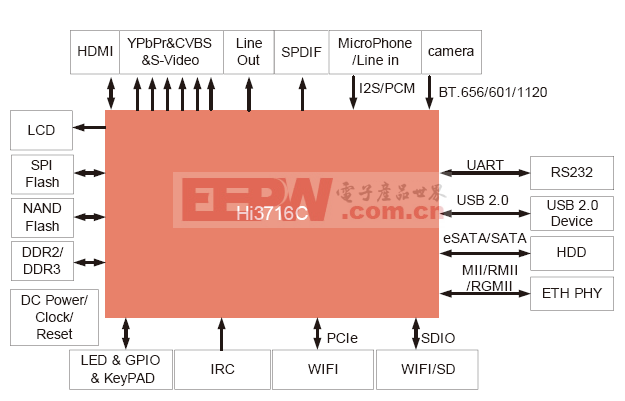

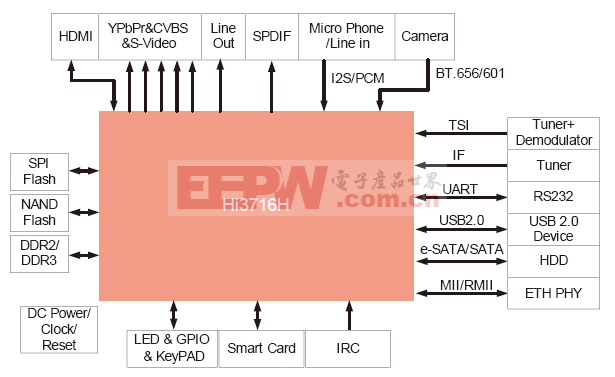

在多裸片设计中,芯片间的互连通过布置在裸片表面的微凸点或混合键合焊盘实现,这些凸点是裸片与中介层、衬底之间的电连接点。现代芯片设计往往需要数十万甚至上百万个此类连接点,且随着裸片数量与互连点的增加,规划和管理这些连接的复杂度也会急剧上升。相关白皮书指出,不合理的凸点规划会对芯片的布线可行性、布线质量及整体设计效率产生负面影响。

传统的凸点规划依靠电子表格、绘图软件等简易图形工具人工完成,这种方式虽适用于早期仅有数千个连接点的单裸片倒装芯片设计,却已无法满足如今大规模多裸片系统的设计需求。人工规划不仅耗时费力,还极易出现人为失误;此外,对某一裸片的凸点布局进行修改后,往往需要对其他裸片或封装设计做出相应调整,若这些更新未能实现有效同步,后续研发环节便可能出现严重的设计错误。

为解决上述问题,现代电子设计自动化(EDA)工具具备了自动化凸点规划功能。设计人员可通过这类工具定义凸点区域 —— 即裸片上用于布置凸点的矩形或不规则区域,且每个区域内的凸点可根据引脚间距、排布间距、对齐方式等约束条件,遵循特定模式进行布置。完成模式定义后,软件便能快速、精准地自动生成数千个凸点;若区域尺寸或设计约束发生变化,凸点布局也会自动更新,大幅节省设计人员的时间与精力。

信号分配是凸点规划的另一核心环节,每个凸点都必须与特定的信号、电源线或接地网络相连。设计人员可手动完成信号分配,也可借助自动化算法,根据线长、布线效率等因素优化凸点布局。自动化信号分配能对整个多裸片系统进行分析,确定信号与凸点的最优映射方式,从而提升芯片整体性能,降低设计复杂度。

除凸点规划外,设计人员还需对硅通孔(TSV) 进行精细规划。硅通孔是贯穿硅基裸片的垂直电连接结构,可实现信号和电源从裸片背面到正面布线层的传输,在多裸片垂直堆叠的 3D 堆叠芯片设计中尤为关键。但硅通孔的结构尺寸相对较大,需要预留足够的排布间距与禁布区,避免对周边电路造成损坏;若硅通孔布局不当,会减少逻辑单元的可用面积,还会对时序性能产生不利影响。因此,设计中必须通过精细规划实现硅通孔的优化布局,同时保证芯片的各项功能不受影响。

现代设计平台将凸点与硅通孔规划整合至统一的设计流程中,工程师可通过二维和三维视图可视化展示各类连接、跟踪工程设计变更,并执行自动化的设计规则检查。借助这类工具,能在设计初期及时发现对齐误差、连接缺失、信号不匹配等问题,从而避免在后续的制造环节产生高成本的失误。

核心结论

凸点与硅通孔的高效规划,是多裸片半导体设计成功的关键所在。随着芯片架构的日趋复杂,人工规划方式已难以满足设计需求。自动化设计工具与规范化的规划方法,能帮助工程师管理数百万个连接点、保证设计精度,并加快产品的上市周期。随着人工智能、高性能计算等先进技术的持续发展,高效的互连规划仍将是现代半导体设计的一项基础要求。

评论