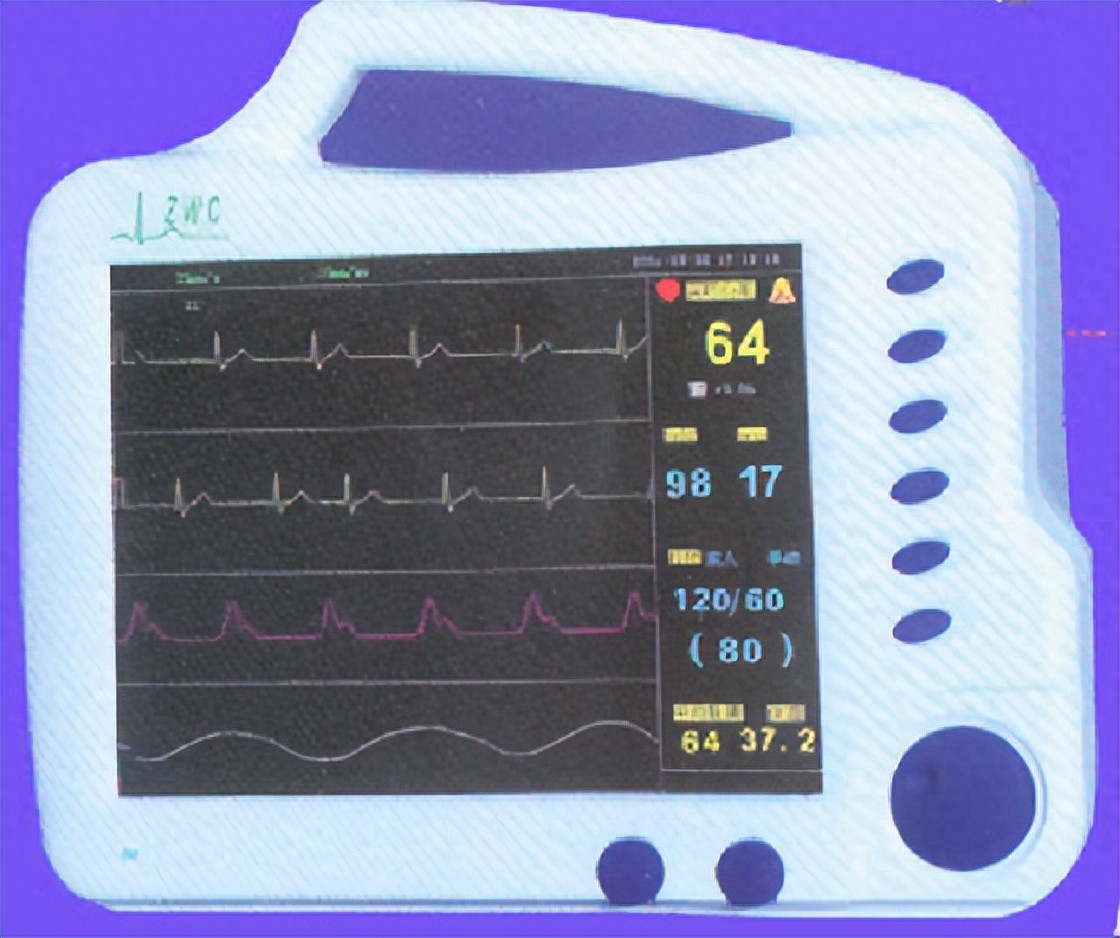

STM32+A3P125 图形控制器方案,多参数监护仪数据采集模块深度解析

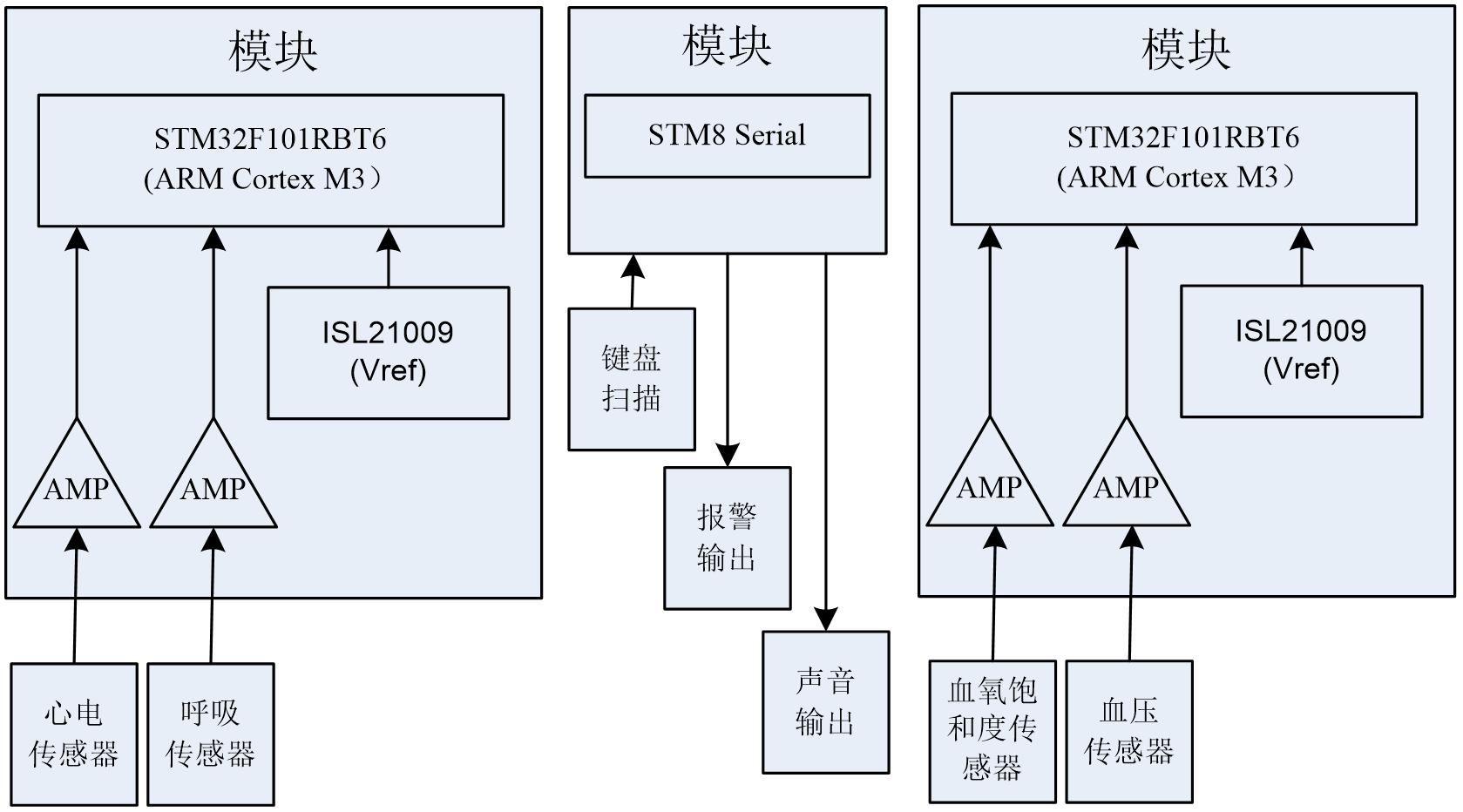

一、生理信号采集与转换架构

多参数监护仪数据采集模块是将人体生理信号转化为数字信号的核心单元,其架构遵循 “传感器感知→信号调理→模数转换→数字处理” 的标准化流程:

1. 传感器类型与生理信号转换

传感器类型 | 生理信号 | 转换原理 | 典型芯片 / 方案 |

ECG 电极阵列 | 心脏电活动 | 体表电位差采集 | 10 电极组合(VR/VL/VF 等)+ INA128 仪表放大器 |

SpO2 指夹探头 | 血氧饱和度 | 660nm 红光 / 940nm 近红外光吸收 | 双波长 LED + 光电二极管(如 APDS-9008) |

NIBP 袖带 | 无创血压 | 振荡法测量袖带压力波动 | MPX5050 压力传感器 + 气泵控制电路 |

热敏电阻 | 体温 | 电阻值随温度变化(如 PT1000) | NTC 热敏电阻 + 恒流源电路 |

有创血压探头 | 有创血压(IBP) | 导管内压力转换为电压信号 | 压阻式压力传感器(如 MS5421) |

呼吸阻抗电极 | 呼吸频率(RESP) | 胸壁电阻抗变化(4~30kHz 激励电流) | 恒流源 + 仪表运放(如 IS |

二、硬件架构与系统定位

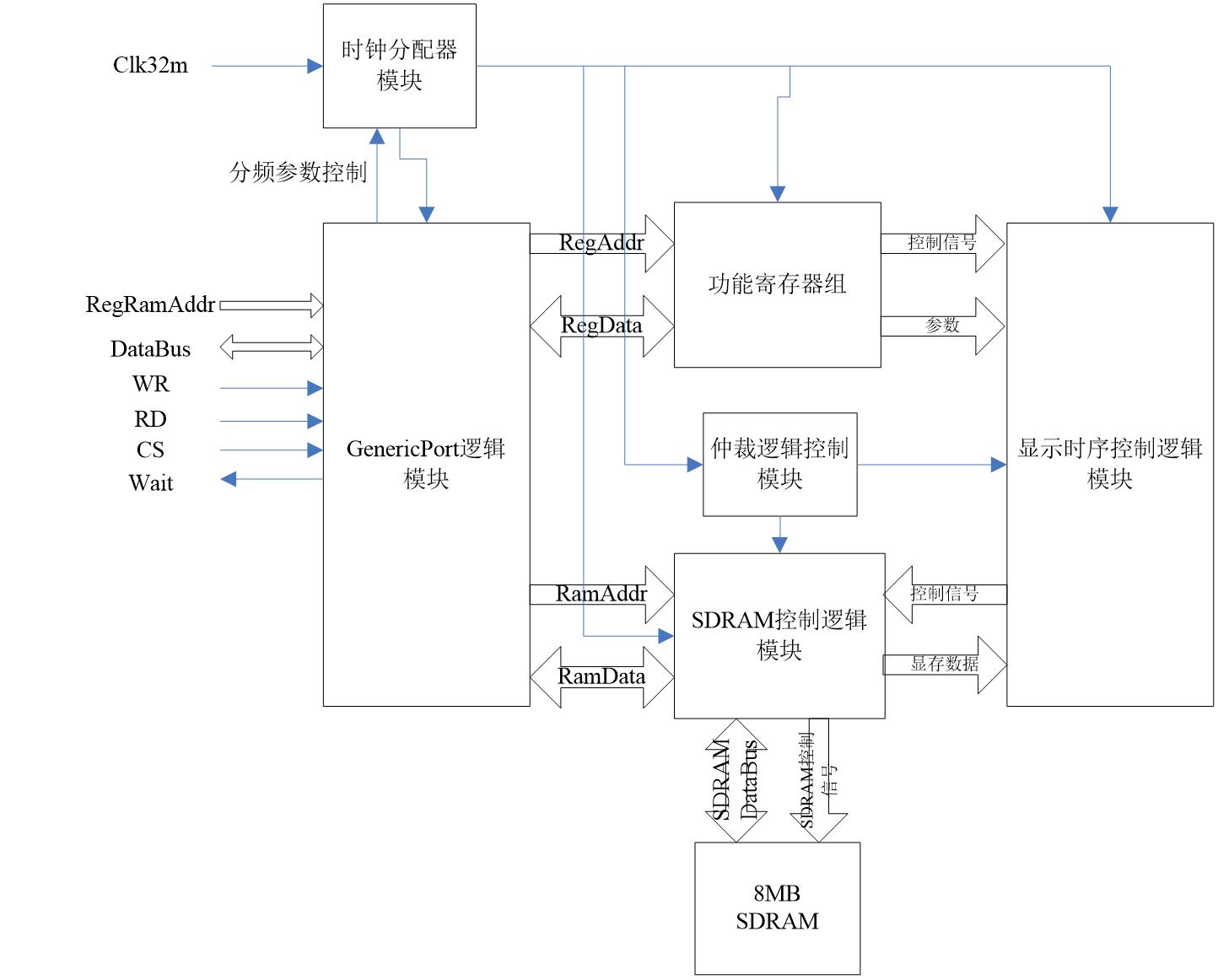

该方案通过 STM32 与 A3P125 FPGA 协同工作,构建适用于医疗监护仪的 LCD/VGA 显示系统,核心优势在于:

STM32 主控:负责参数配置、图形数据传输,采用并行总线与 FPGA 高速通信;

A3P125 FPGA:生成显示时序(像素时钟、行同步、场同步),驱动 LCD/VGA 屏幕实时渲染波形与数据;

应用场景:多参数监护仪的波形显示、菜单界面、趋势图绘制,当前支持 640×480@60Hz VGA 分辨率。

屏显模式(Display Mode)

通信接口:STM32 通过 FSMC 并行总线(8/16 位)与 FPGA 连接,寄存器地址映射如下:

寄存器地址功能描述示例值(640×480)0x00分辨率配置0x02(640×480)0x04刷新率配置0x3C(60Hz)0x08图像缓冲区起始地址0x0000(SDRAM 偏移量)

BMP 数据写入:STM32 将预处理的 BMP 图像数据(如心电波形)按行写入 SDRAM,每像素占用 2 字节(RGB565 格式)。

逻辑框图

时序参数(640×480@60Hz):像素时钟:25.175MHz行时序:总周期 800 像素(640 有效 + 160 消隐)场时序:总周期 525 行(480 有效 + 45 消隐)

SDRAM 控制:FPGA 通过地址计数器按行读取数据,支持突发长度(Burst Length)为 4 的猝发传输,提升数据吞吐量。

三、程序示例与代码框架1. STM32 并行总线配置(FSMC 接口)

/* STM32 FSMC配置 - 16位并行总线 */void FSMC_LCD_Init(void) {

FSMC_NORSRAM_TimingTypeDef Timing = {0};

/* 配置FSMC地址/数据复用模式 */

Timing.AddressSetupTime = 0x0F; // 地址建立时间(15个HCLK周期)

Timing.AddressHoldTime = 0x0F; // 地址保持时间(15个HCLK周期)

Timing.DataSetupTime = 0x3F; // 数据建立时间(63个HCLK周期)

Timing.BusTurnAroundDuration = 0x00; // 总线切换周期(0)

Timing.CLKDivision = 0x00; // 时钟分频(0)

Timing.DataLatency = 0x00; // 数据延迟(0)

Timing.AccessMode = FSMC_ACCESS_MODE_A; // 访问模式A

/* 使能FSMC时钟与GPIO */

__HAL_RCC_FSMC_CLK_ENABLE();

__HAL_RCC_GPIOB_CLK_ENABLE();

__HAL_RCC_GPIOD_CLK_ENABLE();

__HAL_RCC_GPIOE_CLK_ENABLE();

/* 配置FPGA寄存器写函数 */

#define FPGA_REG_ADDR ((uint32_t)0x60000000) // FPGA寄存器基地址

#define FPGA_SDRAM_ADDR ((uint32_t)0x64000000) // SDRAM基地址

/* 示例:写入分辨率寄存器 */

void FPGA_WriteReg(uint8_t reg, uint32_t value) {

*(uint32_t*)(FPGA_REG_ADDR + reg) = value;

}

/* 示例:写入BMP数据到SDRAM */

void FPGA_WriteSDRAM(uint32_t addr, uint16_t* data, uint32_t len) { uint32_t* sdram_ptr = (uint32_t*)(FPGA_SDRAM_ADDR + addr); for (uint32_t i = 0; i < len; i++) {

*sdram_ptr++ = (uint32_t)data[i];

}

}

}

2. A3P125 FPGA 核心代码框架(Verilog)

module vga_controller (

input wire clk_25m, // 25MHz像素时钟

input wire rst_n, // 复位信号

input wire display_en, // 显示使能

input wire [31:0] reg_addr, // 寄存器地址

input wire [31:0] reg_data, // 寄存器数据

input wire reg_we, // 寄存器写使能

// SDRAM接口

output wire [12:0] sdram_addr,

output wire [15:0] sdram_dq,

output wire sdram_cke,

output wire sdram_cs_n,

output wire sdram_ras_n,

output wire sdram_cas_n,

output wire sdram_we_n,

output wire sdram_ldqm,

output wire sdram_udqm,

// VGA接口

output wire vga_hsync, // 行同步

output wire vga_vsync, // 场同步

output wire [15:0] vga_rgb // RGB565色彩);

// 寄存器配置模块

reg [31:0] config_reg[0:15]; // 16个配置寄存器

always @(posedge clk_25m or negedge rst_n) begin

if (!rst_n) begin

// 初始化寄存器

config_reg[0] <= 32'h00000200; // 分辨率640×480

config_reg[1] <= 32'h0000003C; // 刷新率60Hz

end else if (reg_we) begin

config_reg[reg_addr[4:0]] <= reg_data;

end

end

// 显示时序生成模块

reg [11:0] h_counter = 0; // 行计数器(0~799)

reg [11:0] v_counter = 0; // 场计数器(0~524)

wire h_valid = (h_counter >= 0 && h_counter < 640);

wire v_valid = (v_counter >= 0 && v_counter < 480);

wire pixel_valid = h_valid && v_valid;

// 行同步生成

assign vga_hsync = (h_counter >= 656 && h_counter < 752) ? 1'b0 : 1'b1;

// 场同步生成

assign vga_vsync = (v_counter >= 490 && v_counter < 492) ? 1'b0 : 1'b1;

// SDRAM地址计数器

reg [19:0] sdram_addr_counter = 0;

always @(posedge clk_25m or negedge rst_n) begin

if (!rst_n) begin

sdram_addr_counter <= 0;

end else if (display_en && pixel_valid) begin

sdram_addr_counter <= sdram_addr_counter + 1;

end

end

// SDRAM数据读取(简化模型)

assign sdram_addr = sdram_addr_counter[15:3]; // 地址映射

assign sdram_dq = 16'hZZZZ; // 读操作时浮空,实际需控制SDRAM时序

// SDRAM控制信号(简化,实际需完整时序)

assign sdram_cke = 1'b1;

assign sdram_cs_n = ~display_en;

assign sdram_ras_n = 1'b1;

assign sdram_cas_n = display_en && pixel_valid ? 1'b0 : 1'b1;

assign sdram_we_n = 1'b1;

assign sdram_ldqm = 1'b0;

assign sdram_udqm = 1'b0;

// VGA色彩输出(从SDRAM读取数据)

reg [15:0] current_pixel;

always @(posedge clk_25m or negedge rst_n) begin

if (!rst_n) begin

current_pixel <= 16'h0000;

end else if (display_en && pixel_valid) begin

// 实际项目中需通过SDRAM控制器读取数据

current_pixel <= 16'h0000; // 示例值,实际为SDRAM数据

end

end

assign vga_rgb = current_pixel;endmodule

四、开发进展与优化方向

当前成果:完成 640×480 分辨率的 VGA 时序生成;实现 STM32 与 FPGA 的并行总线通信(数据传输速率≥10MB/s);

待改进点:分辨率扩展:支持 1024×768 等更高分辨率,需升级 FPGA 至更大容量型号;显示流畅性:优化 SDRAM 突发传输效率,降低画面撕裂;抗干扰设计:增加 EMI 滤波电路,满足医疗设备电磁兼容性(EMC)要求。

该方案通过 STM32 与 FPGA 的优势互补,在医疗监护仪显示领域实现了高性能与低成本的平衡,尤其适合对实时波形显示有较高要求的场景,如心电图、血氧波形的动态渲染。

评论