FOPLP 热潮加剧:ASE、Powertech 扩张;台积电据报筹备 2026 CoPoS 试验线

根据 经济日报 的报道,扇出型板级封装(FOPLP)被视为先进封装的下一个主流技术。关键行业参与者——包括晶圆巨头台积电、半导体封装和测试领导者 ASE 以及存储封装巨头 Powertech——都在积极投资该领域,以满足来自 NVIDIA 和 AMD 等主要客户对高性能计算(HPC)芯片封装日益增长的需求。

本文引用地址:https://www.eepw.com.cn/article/202506/471405.htm报道中引用的行业消息人士指出,与晶圆级方法相比,板级扇出封装提供了更大的基板面积,并支持异构集成,有助于进一步小型化消费电子产品。

TSMC

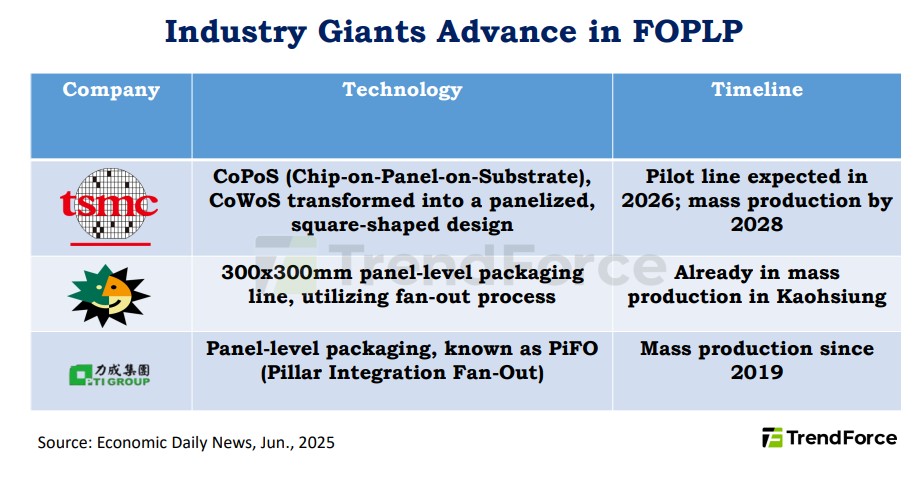

报告称,台积电的扇出型面板级封装(FOPLP)技术据称为 CoPoS(芯片面板基板封装),计划在嘉义生产。报告预计,2026 年将建立一条试验线。

如报告所述,台积电的 CoPoS 技术主要面向人工智能和高性能计算(HPC)应用。消息人士表示,预计到 2028 年将实现大规模生产。该工艺将 CoWoS 封装转换为面板化的方形设计,报告指出这将显著提高芯片产量。

值得注意的是,MoneyDJ 强调英伟达可能是台积电 CoPoS 技术的第一个大客户,而经济日报指出 CoPoS 扩展了为博通设计的 CoWoS-R,以及为英伟达和 AMD 设计的 CoWoS-L。

与此同时,正如经济日报所报道的,台积电在其北美技术研讨会上推出了一种新的 CoWoS 技术,其光罩尺寸为 9.5 倍,计划于 2027 年开始大规模生产。据 Anue 报道,这标志着从目前 CoWoS-L 的 3.3 倍光罩尺寸和去年推出的 8 倍版本的重大升级,能够将 12 个或更多的 HBM 堆叠集成到单个封装中。

正如经济日报所表明的,ASE 已经在高雄运营一条大规模生产的板级封装线,使用 300x300 毫米的板和扇出工艺。

Powertech

该报告还指出,Powertech 在这个领域最为活跃,早在 2019 年就实现了大规模生产。其扇出面板级封装技术,称为 PiFO(柱集成扇出),正如报告所暗示的那样,在技术上与 TSMC 的 CoPoS 类似。

评论