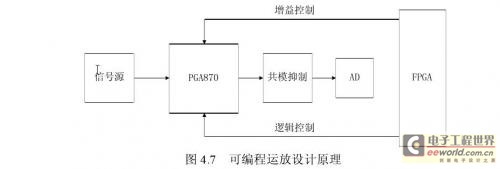

生物电阻抗测量系统中弱信号检测技术研究--弱信号检测调理单元设计与实现

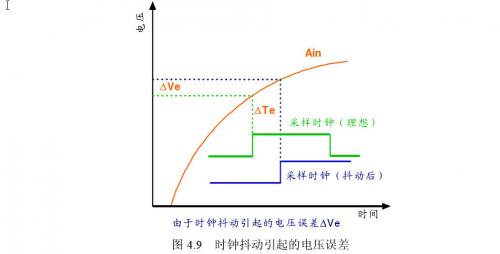

PGA870的增益控制实现方式如表4.4所示,表中未列出全部控制组合,其增益按B0至B5变化组合以0.5dB步进。

4.2.4 ADC前端共模抑制模块

4.2.4.1 ADC前端电路

生物电阻抗测量系统中,信号采集的是直流信号,对于这种信号,不能用阻容耦合或变压器耦合的方式,宜采用直接耦合放大电路但存在零点漂移。所谓零点漂移是指当输人信号为零时,在放大器的输出端出现一个变化不定的输出信号的现象,简称零漂。前级的漂移被后级放大,因此严重干扰正常信号,级数越多,漂移越严重,甚至使放大器不能正常工作。在电路结构上,采用差分电路是目前应用最广泛的能有效抑制零漂的方法。

差分放大电路又叫差分电路,它能有效的减小由于电源波动和晶体管引起的零点漂移,因而获得广泛的应用。

差分电路的输入端有两个信号的输入,这两个信号的差值,为电路有效输入信号,电路的输出是对这两个输入信号之差的放大。设想这样一种情景,如果存在干扰信号,会对两个输入信号产生相同的干扰,通过二者之差,干扰信号的有效输入为零,这就达到了抗共模干扰的目的。

差分放大电路的特点:

1.由两个完全对称的共射电路组合而成。

2.电路采用正负双电源供电。

3.极强的共模抑制能力。

4.2.4.2共模抑制比

为了说明差分放大电路抑制共模信号的能力,常用共模抑制比作为一项技术指标来衡量,其定义为放大器对差模信号的电压放大倍数Aud与对共模信号的电压放大倍数Auc之比,称为共模抑制比,英文全称是Common Mode Rejection Ratio,因此一般用简写CMRR来表示。

差模信号电压放大倍数Aud越大,共模信号电压放大倍数Auc越小,则CMRR越大。此时差分放大电路抑制共模信号的能力越强,放大器的性能越好。当差分放大电路完全对称时,共模信号电压放大倍数Auc=0,则共模抑制比CCMR→∞,这是理想情况,实际上电路完全对称是不存在的,共模抑制比也不可能趋于无穷大。

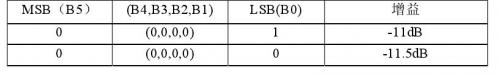

本文采用电路完全对称的差分电路以做到阻抗匹配和ADC前端调理,如图4.8所示:

图中芯片仍为PGA870可变增益放大器,其输出方式为全差分的,能有效的抑制环境中的共模干扰,其CMRR可达到76db,PGA870的输出端采用RC网络进行信号的端接,能有效的减小信号的反射,并采用交流耦合的方式将信号传送至后端ADC芯片。图中信号线ADC_VCM提供差分信号合适的直流偏置,在信号线ADC_IN2+和ADC_IN2-上串接5欧姆的电阻来减小反射过冲电流的大小。

4.3时钟模块设计

4.3.1时钟电路设计分析

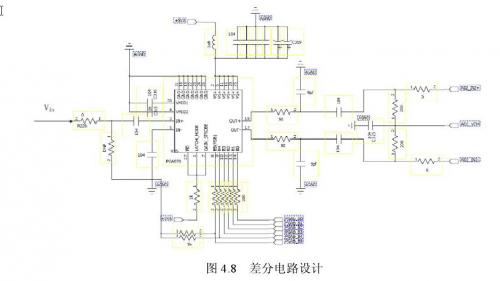

时钟对于高速ADC系统而言尤其关键,这是因为时钟信号的时序准确性可以直接影响ADC的动态特性。理想的时钟源是不会抖动的,因此ADC可以精确的在每个固定的时间间隔进行采集,但是实际电路中各种不确定的因素都会造成时钟的抖动。如图4.9所示,这种时序的不确定性带来的结果是采样波形出现一个为eΔV的误差电压,这相当于在原信号上引入了新的噪声,从而ADC的信噪比会受到数据转换过程的影响。

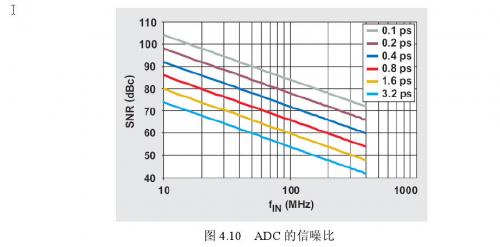

这种噪声反映在ADC的信噪比上就形成了如图4.10所示曲线,随着采样频率的提高,时钟抖动对于系统信噪比的影响越来越大,而同一频率时,高的时钟抖动也比低的时钟抖动给系统带来更多的误差。

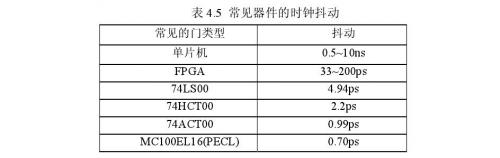

下表4.5是常用的一些器件,在很多设计中倾向于直接由数字器件(FPGA,MCU,DSP)产生一个时钟来作为ADC的采样时钟,这也是为什么ADC精度总是达不到手册上描述的指标的原因,时钟因素制约了系统性能的提高。

典型的高速ADC使用两个时钟脉冲边沿引起各种各样的内部时间信号,并且可能影响到敏感的时钟占空比。通常,为了维护动态性能特征需要容忍5%时间占空比。

AD9216为每个通道提供分开的时钟输入。最好的方案是两个通道的时钟工作在相同的频率和相位上。两个通道的时钟异步时可能使每个通道转换性能有所下降。在某些应用中,相邻两通道之间存在时钟偏差是可以允许的,AD9216当分开的时钟存在输入偏差时(典型值±1ns)不会有重大性能退化,本系统中的AD9216的每个通道都选择相同频率和相位的时钟。

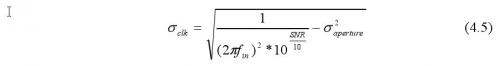

根据抖动和ADC信噪比的关系:

其中,Tσ表示总抖动,clkσ表示采样时钟的抖动,apertureσ表示ADC的孔径抖动,in f代表输入信号频率。

采样时钟的抖动和信噪比的关系可有下述公式导出:

所以一个高质量的时钟源是保证ADC系统精确的关键。在器件的选择上尤其要关注芯片引入的抖动,因此要得到较高的信噪比就要选用抖动较小的时钟源。下面介绍几种常用的ADC时钟设计方案:

评论